MC908AP32CFAE Freescale Semiconductor, MC908AP32CFAE Datasheet - Page 290

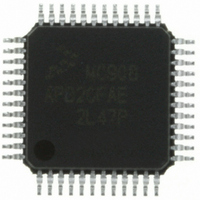

MC908AP32CFAE

Manufacturer Part Number

MC908AP32CFAE

Description

IC MCU 32K FLASH 8MHZ 48-LQFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Specifications of MC908AP32CFAE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, IRSCI, SCI, SPI

Peripherals

LED, LVD, POR, PWM

Number Of I /o

32

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

Controller Family/series

HC08

No. Of I/o's

32

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Embedded Interface Type

I2C, SCI, SPI

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AP32CFAE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC908AP32CFAER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 290 of 324

- Download datasheet (4Mb)

Low-Voltage Inhibit (LVI)

an LVI reset occurs, the MCU remains in reset until V

V

LVIOUT flag in the LVI status register (LVISR).

An LVI reset also drives the RST pin low to provide low-voltage protection to external peripheral devices.

20.3.1 Low V

The low V

below the trip voltage, V

CONFIG1 register.

20.3.2 Low V

The low V

falls below the trip voltage, V

in CONFIG1 register.

20.3.3 Polled LVI Operation

In applications that can operate at V

the LVIOUT bit. In the CONFIG1 register, the LVIPWRD bit must be at logic 0 to enable the LVI module,

and the LVIRSTD bit must be at logic 1 to disable LVI resets.

288

TRIPR2

, which causes the MCU to exit reset. The output of the comparator controls the state of the

DD

REG

V

DETECTOR

DETECTOR

detector circuit monitors the V

LOW V

V

LOW V

REG

detector circuit monitors the V

DD

DD

REG

REG

Detector

DD

Detector

TRIPF1

V

V

V

V

FROM CONFIG1

FROM CONFIG1

DD

DD

REG

REG

TRIPF2

> V

≤ V

LVIPWRD

LVIREGD

> V

≤ V

. The V

Figure 20-2. LVI Module Block Diagram

TRIPR1

TRIPF1

TRIPR2

TRIPF2

MC68HC908AP Family Data Sheet, Rev. 4

. The V

DD

= 1

= 0

= 1

= 0

DD

levels below the V

LVI circuit can be disabled by the setting the LVIPWRD bit in

REG

DD

REG

LVI circuit can be disabled by the setting the LVIREGD bit

voltage and forces a LVI reset when the V

voltage and forces a LVI reset when the V

STOP INSTRUCTION

STOP INSTRUCTION

DD

TRIPF1

rises above V

TO LVISR

FROM CONFIG1

LVIOUT

level, software can monitor V

LVIRSTD

FROM CONFIG1

FROM CONFIG1

TRIPR1

LVISTOP

LVISTOP

and V

LVI RESET

Freescale Semiconductor

REG

rises above

DD

DD

voltage falls

REG

by polling

voltage

Related parts for MC908AP32CFAE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: