SX1211I084TRT Semtech, SX1211I084TRT Datasheet - Page 35

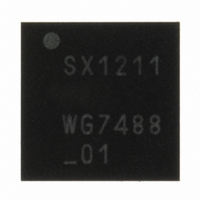

SX1211I084TRT

Manufacturer Part Number

SX1211I084TRT

Description

IC SNGL-CHIP TXRX 32-TQFN

Manufacturer

Semtech

Specifications of SX1211I084TRT

Frequency

860 ~ 960MHz

Data Rate - Maximum

200kbps

Modulation Or Protocol

FSK, OOK

Applications

AMR, ISM, Security and Access

Power - Output

12.5dBm

Sensitivity

-113dBm

Voltage - Supply

2.1 V ~ 3.6 V

Current - Receiving

3mA

Current - Transmitting

25mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Operating Temperature

-40°C ~ 85°C

Package / Case

32-TQFN

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Operating Temperature Classification

Industrial

Modulation Type

FSK/OOK

Package Type

TQFN EP

Operating Supply Voltage (min)

2.1V

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Memory Size

-

Lead Free Status / Rohs Status

Compliant

Other names

SX1211I084TRT

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SX1211I084TRT

Manufacturer:

HITTITE

Quantity:

560

Table 14: Data Operation Mode Selection

Each of these data operation modes is described fully in the following sections.

As illustrated in the Figure 26 below, the SX1211’s SPI interface consists of two sub blocks:

Both interfaces are configured in slave mode whilst the uC is configured as the master. They have separate

selection pins (NSS_CONFIG and NSS_DATA) but share the remaining pins:

As described below, only one interface can be selected at a time with NSS_CONFIG having the priority:

Rev 7 – Sept 2

ADVANCED COMMUNICATIONS & SENSING

5.2. Control Block Description

SPI Config: used in all data operation modes to read and write the configuration registers which control all the

parameters of the chip (operating mode, bit rate, etc...)

SPI Data: used in Buffered and Packet mode to write and read data bytes to and from the FIFO. (FIFO

interrupts can be used to manage the FIFO content.)

SCK (SPI Clock): clock signal provided by the uC

MOSI (Master Out Slave In): data input signal provided by the uC

MISO (Master In Slave Out): data output signal provided by the SX1211

MCParam_Data_mode

5.2.1. SPI Interface

Registers

Registers

Config.

Config.

nd

FIFO

, 2008

00

01

1x

5.2.1.1. Overview

SX1211

Data Operation Mode

Figure 26: SPI Interface Overview and uC Connections

Continuous

Buffered

Packet

CONFIG

(slave)

(slave)

SPI

DATA

SPI

Page 35 of 92

NSS_CONFIG

MOSI

MISO

SCK

NSS_DATA

NSS_DATA

MOSI

MISO

SCK

NSS_CONFIG

(master)

µ C

www.semtech.com

SX1211