SX1211I084TRT Semtech, SX1211I084TRT Datasheet - Page 45

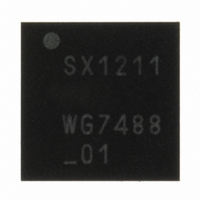

SX1211I084TRT

Manufacturer Part Number

SX1211I084TRT

Description

IC SNGL-CHIP TXRX 32-TQFN

Manufacturer

Semtech

Specifications of SX1211I084TRT

Frequency

860 ~ 960MHz

Data Rate - Maximum

200kbps

Modulation Or Protocol

FSK, OOK

Applications

AMR, ISM, Security and Access

Power - Output

12.5dBm

Sensitivity

-113dBm

Voltage - Supply

2.1 V ~ 3.6 V

Current - Receiving

3mA

Current - Transmitting

25mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Operating Temperature

-40°C ~ 85°C

Package / Case

32-TQFN

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Operating Temperature Classification

Industrial

Modulation Type

FSK/OOK

Package Type

TQFN EP

Operating Supply Voltage (min)

2.1V

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Memory Size

-

Lead Free Status / Rohs Status

Compliant

Other names

SX1211I084TRT

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SX1211I084TRT

Manufacturer:

HITTITE

Quantity:

560

If the transmitter is switched off (for example due to entering another chip mode) during transmission it will stop

immediately, even if there is still unsent data.

Figure 39 illustrates Tx processing with a 16 byte FIFO depth and Tx_start_irq_0=0. Please note that in this

example the packet length is equal to FIFO size, but this does not need to be the case, the uC can use the FIFO

interrupts anytime during Tx to manage FIFO contents and write additional bytes.

After entering Rx in Buffered mode, the chip requires the uC to retrieve the received data from the FIFO. The FIFO

will actually start being filled with received bytes either; when a Sync word has been detected (in this case only the

bytes following the Sync word are filled into the FIFO) or when the Fifo_fill bit is asserted by the user - depending

on the state of bit, IRQParam_Fifo_fill_method.

In Buffered mode, the packet length is not limited i.e. as long as Fifo_fill is set, the received bytes are shifted into

the FIFO.

The uC software must therefore manage the transfer of the FIFO contents by interrupt and ensure reception of the

correct number of bytes. (In this mode, even if the remote transmitter has stopped, the demodulator will output

random bits from noise)

When the FIFO is full, Fifofull IRQ source is asserted to alert the uC, that at that time, the FIFO can still be unfilled

without data loss. If the FIFO is not unfilled, once the SR is also full (i.e. 8 bits periods later) Fifo_overrun_clr is

asserted and SR’s content is lost.

Figure 40 illustrates an Rx processing with a 16 bytes FIFO size and Fifo_fill_method=0. Please note that in the

illustrative example of section 5.4.6, the uC does not retrieve any byte from the FIFO through SPI Data, causing

overrun.

Rev 7 – Sept 2

ADVANCED COMMUNICATIONS & SENSING

FIFO

15

Data Tx

(from SR)

Start condition

(Cf. Tx_start_irq_0)

Tx_done

0

Fifofull

/Fifoempty

5.4.3. Rx Processing

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

nd

, 2008

Figure 39: Tx processing in Buffered Mode (FIFO size = 16, Tx_start_irq_0=0)

XXX

SPI Data

from

b0

b1

b2

Page 45 of 92

b3

b4

b5

b6

b7

b8

b9

b10 b11

b12 b13

b14 b15

www.semtech.com

SX1211

XXX