M48T86MH1 STMicroelectronics, M48T86MH1 Datasheet - Page 10

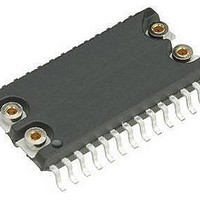

M48T86MH1

Manufacturer Part Number

M48T86MH1

Description

Real Time Clock USE 511-M48T86MH1E

Manufacturer

STMicroelectronics

Datasheet

1.M48T86MH1.pdf

(36 pages)

Specifications of M48T86MH1

Function

Clock, Calendar, Interrupt, Alarm

Rtc Memory Size

128 B

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4.5 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Rtc Bus Interface

Multiplexed

Package / Case

SO-28

Time Format

HH:MM:SS, Binary

Date Format

DW:DM:M:Y, Binary

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M48T86MH1

Manufacturer:

CARTYS

Quantity:

2 585

Part Number:

M48T86MH1

Manufacturer:

ST

Quantity:

20 000

Operation

2.1.5

2.1.6

2.1.7

2.1.8

2.1.9

2.1.10

10/36

MOT (mode select)

The MOT pin offers the flexibility to choose between two bus types (see

page

or left disconnected, Intel bus timing is selected. The pin has an internal pull-down

resistance of approximately 20 K .

DS (data strobe input)

The DS pin is also referred to as READ (RD). A falling edge transition on the Data Strobe

(DS) input enables the output during a a READ cycle. This is very similar to an Output

Enable (G) signal on other memory devices.

E (chip enable input)

The chip enable pin must be asserted low for a bus cycle in the M48T86 to be accessed.

Bus cycles which take place without asserting E will latch the addresses present, but no

data access will occur.

IRQ (interrupt request output)

The IRQ pin is an open drain output that can be used as an interrupt input to a processor.

The IRQ output remains low as long as the status bit causing the interrupt is present and the

corresponding interrupt-enable bit is set. IRQ returns to a high impedance state whenever

Register C is read. The RST pin can also be used to clear pending interrupts. The IRQ bus

is an open drain output so it requires an external pull-up resistor to V

RST (reset input)

The M48T86 is reset when the RST input is pulled low. With a valid V

on RST, the following events occur:

1.

2.

3.

4.

5.

6.

7.

8.

9.

10. Update Ended Interrupt Enable (UIE) is cleared to a zero (Register B; Bit 4).

RCL (RAM clear)

The RCL pin is used to clear all 114 storage bytes, excluding clock and control registers, of

the array to FF(hex) value. The array will be cleared when the RCL pin is held low for at least

100 ms with the oscillator running. Usage of this pin does not affect battery load. This

function is applicable only when V

Periodic Interrupt Enable (PIE) bit is cleared to a zero (Register B; Bit 6);

Alarm Interrupt Enable (AIE) bit is cleared to a zero (Register B; Bit 5);

Update Ended Interrupt Request (UF) bit is cleared to a zero (Register C; Bit 4);

Interrupt Request (IRQF) bit is cleared to a zero (Register C Bit 7);

Periodic Interrupt Flag (PF) bit is cleared to a zero (Register C; Bit 6);

The device is not accessible until RST is returned high;

Alarm Interrupt Flag (AF) bit is cleared to a zero (Register C; Bit 5);

The IRQ pin is in the high impedance state

Square Wave Output Enable (SQWE) bit is cleared to zero (Register B; Bit 3); and

12). When connected to V

CC

CC

, Motorola bus timing is selected. When connected to V

is applied.

CC

CC

.

Figure 7 on

applied and a low

M48T86

SS