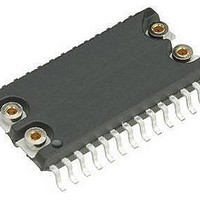

M48T86MH1 STMicroelectronics, M48T86MH1 Datasheet - Page 17

M48T86MH1

Manufacturer Part Number

M48T86MH1

Description

Real Time Clock USE 511-M48T86MH1E

Manufacturer

STMicroelectronics

Datasheet

1.M48T86MH1.pdf

(36 pages)

Specifications of M48T86MH1

Function

Clock, Calendar, Interrupt, Alarm

Rtc Memory Size

128 B

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4.5 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Rtc Bus Interface

Multiplexed

Package / Case

SO-28

Time Format

HH:MM:SS, Binary

Date Format

DW:DM:M:Y, Binary

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M48T86MH1

Manufacturer:

CARTYS

Quantity:

2 585

Part Number:

M48T86MH1

Manufacturer:

ST

Quantity:

20 000

M48T86

3.5

3.6

3.7

3.8

Alarm interrupt

The alarm interrupt provides the system processor with an interrupt when a match is made

between the RTC's hours, minutes, and seconds bytes and the corresponding alarm bytes.

The three alarm bytes can be used in two ways. First, when the alarm time is written in the

appropriate hours, minutes, and seconds alarm locations, the alarm interrupt is initiated at

the specified time each day if the Alarm Interrupt Enable bit (Register B; Bit 5) is high. The

second use is to insert a “Don't care” state in one or more of the three alarm bytes. The

“Don't care” code is any hexadecimal value from C0 to FF. The two most significant bits of

each byte set the “Don't care” condition when at logic '1.' An alarm will be generated each

hour when the “Don't care” is are set in the hours byte. Similarly, an alarm is generated

every minute with “Don't care” codes in the hour and minute alarm bytes. The “Don't care”

codes in all three alarm bytes create an interrupt every second.

Update cycle interrupt

After each update cycle, the Update Cycle Ended Flag bit (UF) (Register C; Bit 4) is set to a

'1.' If the Update Interrupt Enable bit (UIE) (Register B; Bit 4) is set to a '1,' and the SET bit

(Register B; Bit 7) is a '0,' then an interrupt request is generated at the end of each update

cycle.

Oscillator control bits

When the M48T86 is shipped from the factory the internal oscillator is turned off. This

feature prevents the lithium energy cell from being discharged until it is installed in a system.

A pattern of “010” in Bits 4-6 of Register A will turn the oscillator on and enable the

countdown chain. A pattern of “11X” will turn the oscillator on, but holds the countdown

chain of the oscillator in reset. All other combinations of Bits 4-6 keep the oscillator off.

Update cycle

The M48T86 executes an update cycle once per second regardless of the SET bit (Register

B; Bit 7). When the SET bit is asserted, the user copy of the double buffered time, calendar,

and alarm bytes is frozen and will not update as the time increments. However, the time

countdown chain continues to update the internal copy of the buffer. This feature allows

accurate time to be maintained, independent of reading and writing the time, calendar, and

alarm buffers. This also guarantees that the time and calendar information will be

consistent. The update cycle also compares each alarm byte with the corresponding time

byte and issues an alarm if a match or if a “Don't care” code is present in all three positions.

There are three methods of accessing the real time clock that will avoid any possibility of

obtaining inconsistent time and calendar data. The first method uses the update-ended

interrupt. If enabled, an interrupt occurs after every update cycle which indicates that over

999ms are available to read valid time and date information. If this interrupt is used, the

IRQF Bit (Register C; Bit 7) should be cleared before leaving the interrupt routine.

A second method uses the Update-In-Progress (UIP) bit (Register A; Bit 7) to determine if

the update cycle is in progress. The UIP bit will pulse once per second. After the UIP bit

goes high, the update transfer occurs 244 µs later. If a low is read on the UIP bit, the user

has at least 244 µs before the time/calendar data will be changed. Therefore, the user

Clock operations

17/36