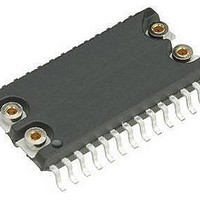

M48T86MH1 STMicroelectronics, M48T86MH1 Datasheet - Page 16

M48T86MH1

Manufacturer Part Number

M48T86MH1

Description

Real Time Clock USE 511-M48T86MH1E

Manufacturer

STMicroelectronics

Datasheet

1.M48T86MH1.pdf

(36 pages)

Specifications of M48T86MH1

Function

Clock, Calendar, Interrupt, Alarm

Rtc Memory Size

128 B

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4.5 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Rtc Bus Interface

Multiplexed

Package / Case

SO-28

Time Format

HH:MM:SS, Binary

Date Format

DW:DM:M:Y, Binary

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M48T86MH1

Manufacturer:

CARTYS

Quantity:

2 585

Part Number:

M48T86MH1

Manufacturer:

ST

Quantity:

20 000

Clock operations

3.3

3.4

16/36

Interrupts

The RTC plus RAM includes three separate, fully automatic sources of interrupt (alarm,

periodic, update-in-progress) available to a processor. The alarm interrupt can be

programmed to occur at rates from once per second to once per day. The periodic interrupt

can be selected from rates of 500 ms to 122 µs. The update-ended interrupt can be used to

indicate that an update cycle has completed.

The processor program can select which interrupts, if any, are going to be used. Three bits

in Register B enable the interrupts. Writing a logic '1' to an interrupt-enable bit (Register B;

Bit 6 = PIE; Bit 5 = AIE; Bit 4 = UIE) permits an interrupt to be initialized when the event

occurs. A '0' in an interrupt-enable bit prohibits the IRQ pin from being asserted from that

interrupt condition. If an interrupt flag is already set when an interrupt is enabled, IRQ is

immediately set at an active level, although the interrupt initiating the event may have

occurred much earlier. As a result, there are cases where the program should clear such

earlier initiated interrupts before first enabling new interrupts.

When an interrupt event occurs, the related flag bit (Register C; Bit 6 = PF; Bit 5 = AF;

Bit 4 = UF) is set to a logic '1.' These flag bits are set independent of the state of the

corresponding enable bit in Register B and can be used in a polling mode without enabling

the corresponding enable bits. The interrupt flag bits are status bits which software can

interrogate as necessary.

When a flag is set, an indication is given to software that an interrupt event has occurred

since the flag bit was last read; however, care should be taken when using the flag bits as all

are cleared each time Register C is read. Double latching is included with Register C so that

bits which are set remain stable throughout the READ cycle. All bits which are set high are

cleared when read. Any new interrupts which are pending during the READ cycle are held

until after the cycle is completed. One, two, or three bits can be set when reading Register

C. Each utilized flag bit should be examined when read to ensure that no interrupts are lost.

The second flag bit usage method is with fully enabled interrupts. When an interrupt flag bit

is set and the corresponding enable bit is also set, the IRQ pin is asserted low. IRQ is

asserted as long as at least one of the three interrupt sources has its flag and enable bits

both set. The IRQF bit (Register C; Bit 7) is a '1' whenever the IRQ pin is being driven low.

Determination that the RTC initiated an interrupt is accomplished by reading Register C. A

logic '1' in the IRQF bit indicates that one or more interrupts have been initiated by the

M48T86. The act of reading Register C clears all active flag bits and the IRQF bit.

Periodic interrupt

The periodic interrupt will cause the IRQ pin to go to an active state from once every 500 ms

to once every 122 µs. This function is separate from the alarm interrupt which can be output

from once per second to once per day. The periodic interrupt rate is selected using the same

Register A bits which select the square wave frequency (see

the Register A bits affects both the square wave frequency and the periodic interrupt output.

However, each function has a separate enable bit in Register B. The periodic interrupt is

enabled by the PIE bit (Register B; Bit 6). The periodic interrupt can be used with software

counters to measure inputs, create output intervals, or await the next needed software

function.

Table 4 on page

18). Changing

M48T86