DSP56301AG80 Freescale Semiconductor, DSP56301AG80 Datasheet - Page 51

DSP56301AG80

Manufacturer Part Number

DSP56301AG80

Description

IC DSP 24BIT 80MHZ GP 208-LQFP

Manufacturer

Freescale Semiconductor

Series

DSP563xxr

Type

Fixed Pointr

Specifications of DSP56301AG80

Interface

Host Interface, SSI, SCI

Clock Rate

80MHz

Non-volatile Memory

ROM (9 kB)

On-chip Ram

24kB

Voltage - I/o

3.30V

Voltage - Core

3.30V

Operating Temperature

-40°C ~ 100°C

Mounting Type

Surface Mount

Package / Case

208-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DSP56301AG80

Manufacturer:

CONEXANT

Quantity:

4 200

Company:

Part Number:

DSP56301AG80

Manufacturer:

FREESCALE

Quantity:

7

Company:

Part Number:

DSP56301AG80

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

DSP56301AG80B1

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Freescale Semiconductor

Notes:

No.

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

CAS deassertion pulse width

Row address valid to RAS assertion

RAS assertion to row address not valid

Column address valid to CAS assertion

CAS assertion to column address not valid

RAS assertion to column address not valid

Column address valid to RAS deassertion

WR deassertion to CAS assertion

CAS deassertion to WR

RAS deassertion to WR

CAS assertion to WR deassertion

RAS assertion to WR deassertion

WR assertion pulse width

WR assertion to RAS deassertion

WR assertion to CAS deassertion

Data valid to CAS assertion (write)

CAS assertion to data not valid (write)

RAS assertion to data not valid (write)

WR assertion to CAS assertion

CAS assertion to RAS assertion (refresh)

RAS deassertion to CAS assertion (refresh)

RD assertion to RAS deassertion

RD assertion to data valid

RD deassertion to data not valid

WR assertion to data active

WR deassertion to data high impedance

1.

2.

3.

4.

Table 2-14.

The number of wait states for an out-of-page access is specified in the DCR.

The refresh period is specified in the DCR.

RD deassertion always occurs after CAS deassertion; therefore, the restricted timing is t

Either t

RCH

Characteristics

or t

RRH

4

4

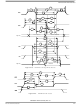

DRAM Out-of-Page and Refresh Timings, Fifteen Wait States

assertion

assertion

must be satisfied for read cycles.

3

3

DSP56301 Technical Data, Rev. 10

Symbol

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

WCH

WCR

WCS

RCH

RRH

t

RWL

CWL

t

DHR

ROH

t

t

ASR

RAH

ASC

CAH

t

RAL

RCS

t

CSR

RPC

t

WP

CP

AR

DS

DH

GA

GZ

15.75 × T

14.25 × T

1.75 × T

0.75 × T

6.25 × T

6.25 × T

2.75 × T

0.75 × T

6.25 × T

9.75 × T

0.25 × T

0.25 × T

15.5 × T

8.75 × T

6.25 × T

9.75 × T

4.75 × T

15.5 × T

Expression

9.5 × T

9.5 × T

1.5 × T

14 × T

14 × T

7 × T

5 × T

6 × T

100 MHz:

100 MHz:

0.25 × T

80 MHz:

80 MHz:

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

− 4.0

− 3.8

− 4.2

C

C

− 6.5

− 5.7

− 4.2

− 4.3

− 4.0

– 6.0

− 4.0

− 4.0

− 4.0

− 4.0

− 4.0

– 3.7

− 2.6

− 2.0

− 4.5

− 4.0

− 4.0

− 4.0

− 4.0

− 4.0

– 1.5

− 4.3

− 4.3

C

117.9

114.6

189.3

192.6

173.8

105.4

117.9

114.5

189.8

Min

74.1

74.1

30.4

74.1

83.5

58.7

18.2

70.8

74.1

14.8

55.4

OFF

5.4

0.5

0.0

9.1

—

—

—

—

80 MHz

AC Electrical Characteristics

and not t

1, 2

168.5

Max

3.1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

(Continued)

GZ

.

150.5

153.2

138.2

151.0

Min

56.5

58.5

23.5

58.5

93.5

66.0

46.2

13.8

55.8

90.8

83.5

58.5

93.5

90.7

11.0

43.5

3.5

0.5

0.0

6.0

—

—

—

—

100 MHz

134.3

Max

2.5

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Unit

2-25

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns