KSZ8851-16MLL-EVAL Micrel Inc, KSZ8851-16MLL-EVAL Datasheet - Page 30

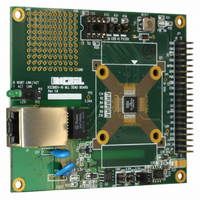

KSZ8851-16MLL-EVAL

Manufacturer Part Number

KSZ8851-16MLL-EVAL

Description

BOARD EVALUATION KSZ8851-16MLL

Manufacturer

Micrel Inc

Series

LinkMD®r

Specifications of KSZ8851-16MLL-EVAL

Main Purpose

Interface, Ethernet Controller (PHY and MAC)

Embedded

No

Utilized Ic / Part

KSZ8851-16MLL

Primary Attributes

1 Port, 100BASE-TX/10BASE-T

Secondary Attributes

8/16-Bit Interface, LinkMD Cable Diagnostics

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-3292

Micrel, Inc.

KSZ8851-16MLL/MLLI

Driver Routine for Receive Packet from KSZ8851-16MLL to Host Processor

The software driver receives data packet frames from the KSZ8851-16MLL device either as a result of polling or an

interrupt based service. When an interrupt is received, the OS invokes the interrupt service routine that is in the interrupt

vector table.

If your system has OS support, to minimize interrupt lockout time, the interrupt service routine should handle at interrupt

level only those tasks that require minimum execution time, such as error checking or device status change. The routine

should queue all the time-consuming work to transfer the packet from the KSZ8851-16MLL RXQ into system memory at

task level. The following Figure 9 shows the step-by-step for receive packets from KSZ8851-16MLL to host processor.

Note: Each DMA read operation from the host CPU to read RXQ frame buffer, the first read data (byte in 8-bit bus mode,

word in 16-bit bus mode and double word in 32-bit bus mode) is dummy data and must be discarded by host CPU.

Afterward, host CPU must read each frame data to align with double word boundary at end. For example, the host CPU

has to read up to 68 bytes if received frame is 65 bytes.

Figure 9. Host RX Single or Multiple Frames in Auto-Dequeue Flow Diagram

August 2009

30

M9999-083109-2.0