KSZ8851-16MLL-EVAL Micrel Inc, KSZ8851-16MLL-EVAL Datasheet - Page 40

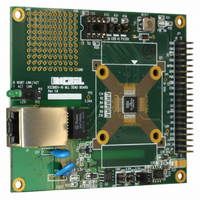

KSZ8851-16MLL-EVAL

Manufacturer Part Number

KSZ8851-16MLL-EVAL

Description

BOARD EVALUATION KSZ8851-16MLL

Manufacturer

Micrel Inc

Series

LinkMD®r

Specifications of KSZ8851-16MLL-EVAL

Main Purpose

Interface, Ethernet Controller (PHY and MAC)

Embedded

No

Utilized Ic / Part

KSZ8851-16MLL

Primary Attributes

1 Port, 100BASE-TX/10BASE-T

Secondary Attributes

8/16-Bit Interface, LinkMD Cable Diagnostics

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-3292

Register Map: MAC, PHY and QMU

Do not write to bit values or to registers defined as Reserved. Manipulating reserved bits or registers causes

unpredictable and often fatal results. If the user wants to write to these reserved bits, the user has to read back these

reserved bits (RO or RW) first, then “OR” with the read value of the reserved bits and write back to these reserved bits.

Bit Type Definition

RO = Read only.

WO = Write only.

RW = Read/Write.

W1C = Write 1 to Clear (writing an “1” to clear this bit).

0x00 – 0x07: Reserved

Chip Configuration Register (0x08 – 0x09): CCR

This register indicates the chip configuration mode based on strapping and bonding options

0x0A – 0x0F: Reserved

Host MAC Address Registers: MARL, MARM and MARH

These Host MAC address registers are loaded starting at word location 0x1 of the EEPROM upon hardware reset. The

software driver can read or write these registers value, but it will not modify the original Host MAC address value in the

EEPROM. These six bytes of Host MAC address in external EEPROM are loaded to these three registers as mapping

below:

MARL[15:0] = EEPROM 0x1(MAC Byte 2 and 1)

MARM[15:0] = EEPROM 0x2(MAC Byte 4 and 3)

August 2009

Micrel, Inc.

Bit

15-11

10

9

8

7

6

5

4

3

2

1

0

-

-

-

0

-

-

0

-

0

0

-

0

Default Value

R/W

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

Description

Reserved.

Bus Endian mode

The EESK (pin 10) value is latched into this bit druing power-up/reset.

0: Bus in Big Endian mode, 1: Bus in Little Endian mode.

EEPROM presence

The EED_IO (pin 9) value is latched into this bit druing power-up/reset.

0: No external EEPROM, 1: Use external EEPROM.

Reserved.

8-Bit data bus width

This bit value is loaded from P1LED1 (pin 1)

0: Not in 8-bit bus mode operation, 1: In 8-bit bus mode operation.

16-Bit data bus width

This bit value is loaded from P1LED1 (pin 1)

0: Not in 16-bit bus mode operation, 1: In 16-bit bus mode operation.

Reserved.

Shared data bus mode for data and address

0: Data and address bus are seperated.

1: Data and address bus are shared.

Reserved.

Reserved.

48-Pin Chip Package

To indicate chip package is 48-pin.

0: No, 1: Yes.

Reserved.

40

KSZ8851-16MLL/MLLI

M9999-083109-2.0