KSZ8851-16MLL-EVAL Micrel Inc, KSZ8851-16MLL-EVAL Datasheet - Page 33

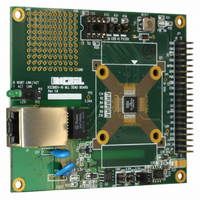

KSZ8851-16MLL-EVAL

Manufacturer Part Number

KSZ8851-16MLL-EVAL

Description

BOARD EVALUATION KSZ8851-16MLL

Manufacturer

Micrel Inc

Series

LinkMD®r

Specifications of KSZ8851-16MLL-EVAL

Main Purpose

Interface, Ethernet Controller (PHY and MAC)

Embedded

No

Utilized Ic / Part

KSZ8851-16MLL

Primary Attributes

1 Port, 100BASE-TX/10BASE-T

Secondary Attributes

8/16-Bit Interface, LinkMD Cable Diagnostics

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-3292

- Current page: 33 of 79

- Download datasheet (544Kb)

Micrel, Inc.

KSZ8851-16MLL/MLLI

CPU Interface I/O Registers

The KSZ8851-16MLL provides an SRAM-like asynchronous bus interface for the CPU to access its internal I/O registers.

I/O registers serve as the address that the microprocessor uses when communicating with the device. This is used for

configuring operational settings, reading or writing control, status information, and transferring packets. The KSZ8851-

16MLL can be programmed to interface with either Big-Endian or Little-Endian processor.

I/O Registers

The following I/O Space Mapping Tables apply to 8 or 16-bit bus interface. Depending upon the bus mode selected, each

I/O access can be performed the following operations:

In 8-bit bus mode, there are 256 address locations which is based on SD[7:0] for address when CMD=1. The SD[7:0] is

for data when CMD=0.

In 16-bit bus mode, there are 64 address locations which is based on SD[7:2] ([1:0] is “don’t care”) for address and

SD[15:12] for Byte Enable BE[3:0] (either one byte or two bytes) when CMD=1. The SD[15:0] is for data when CMD=0.

August 2009

33

M9999-083109-2.0

Related parts for KSZ8851-16MLL-EVAL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

10/100BT Ethernet MAC + PHY With Generic (8, 16-bit) Bus Interface (I-Temp)

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

10/100BT Ethernet MAC + PHY With Generic (8, 16-bit) Bus Interface (I-Temp)

Manufacturer:

Micrel Inc

Part Number:

Description:

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

Single Ethernet Port + Generic (16-bit) Bus Interface( ) Eval Board

Manufacturer:

Micrel Inc

Part Number:

Description:

IC CTLR MAC/PHY NON PCI 128PQFP

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

IC CTLR MAC 1PORT NON-PCI 48LQFP

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

IC CTLR MAC/PHY NON-PCI 128-PQFP

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

10/100BT Ethernet MAC + PHY With Generic (32-bit) Bus Interface

Manufacturer:

Micrel Inc

Datasheet:

Part Number:

Description:

Single-port Ethernet Mac Controller With 8/16-bit Or 32-bit Non-pci Interface

Manufacturer:

Micrel Semiconductor

Datasheet:

Part Number:

Description:

Single-Port Ethernet MAC Controller with 8-Bit or 16-Bit Non-PCI Interface

Manufacturer:

MICREL [Micrel Semiconductor]

Datasheet:

Part Number:

Description:

Ethernet ICs Single-Port Ethernet Controller (Automotive Grade)

Manufacturer:

Micrel

Datasheet:

Part Number:

Description:

Ethernet ICs Single-Port Ethernet Controller (Automotive Grade)

Manufacturer:

Micrel

Datasheet:

Part Number:

Description:

Manufacturer:

Micrel Inc

Datasheet: