KSZ8851-16MLL-EVAL Micrel Inc, KSZ8851-16MLL-EVAL Datasheet - Page 47

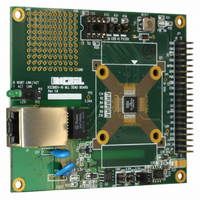

KSZ8851-16MLL-EVAL

Manufacturer Part Number

KSZ8851-16MLL-EVAL

Description

BOARD EVALUATION KSZ8851-16MLL

Manufacturer

Micrel Inc

Series

LinkMD®r

Specifications of KSZ8851-16MLL-EVAL

Main Purpose

Interface, Ethernet Controller (PHY and MAC)

Embedded

No

Utilized Ic / Part

KSZ8851-16MLL

Primary Attributes

1 Port, 100BASE-TX/10BASE-T

Secondary Attributes

8/16-Bit Interface, LinkMD Cable Diagnostics

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-3292

Wakeup Frame 3 CRC1 Register (0x62 – 0x63): WF3CRC1

This register contains the expected CRC values of the Wake up frame 3 pattern. The value of the CRC calculated is

based on the IEEE 802.3 Ethernet standard, it is taken over the bytes specified in the wake-up byte mask registers.

Wakeup Frame 3 Byte Mask 0 Register (0x64 – 0x65): WF3BM0

This register contains the first 16 bytes mask values of the Wake up frame 3 pattern. Setting bit 0 selects the first byte

of the Wake up frame 3, setting bit 15 selects the 16th byte of the Wake up frame 3.

Wakeup Frame 3 Byte Mask 1 Register (0x66 – 0x67): WF3BM1

This register contains the next 16 bytes mask values of the Wake up frame 3 pattern. Setting bit 0 selects the 17th byte

of the Wake up frame 3. Setting bit 15 selects the 32nd byte of the Wake up frame 3.

Wakeup Frame 3 Byte Mask 2 Register (0x68 – 0x69): WF3BM2

This register contains the next 16 bytes mask values of the Wake up frame 3 pattern. Setting bit 0 selects the 33rd byte

of the Wake up frame 3. Setting bit 15 selects the 48th byte of the Wake up frame 3.

Wakeup Frame 3 Byte Mask 3 Register (0x6A – 0x6B): WF3BM3

This register contains the last 16 bytes mask values of the Wake up frame 3 pattern. Setting bit 0 selects the 49th byte

of the Wake up frame 3. Setting bit 15 selects the 64th byte of the Wake up frame 3.

0x6C – 0x6F: Reserved

Transmit Control Register (0x70 – 0x71): TXCR

This register holds control information programmed by the CPU to control the QMU transmit module function.

August 2009

Micrel, Inc.

Bit

15-0

Bit

15-0

Bit

15-0

Bit

15-0

Bit

15-0

Bit

15-9

8

7

-

0x0

0x0

Default Value

0

Default Value

0

Default Value

0

Default Value

0

Default Value

0

Default Value

R/W

RW

R/W

RW

R/W

RW

R/W

RW

R/W

RW

R/W

RO

RW

RO

Description

WF3CRC1

Wake-up frame 3 CRC (upper 16 bits). The expected CRC value of a Wake up frame

3 pattern.

Description

WF3BM0

Wake up Frame 3 Byte Mask 0. The first 16 byte mask of a Wake up frame 3 pattern.

Description

WF3BM1

Wake up Frame 3 Byte Mask 1. The next 16 bytes mask covering bytes 17 to 32 of a

Wake up frame 3 pattern.

Description

WF3BM2

Wake up Frame 3 Byte Mask 2. The next 16 bytes mask covering bytes 33 to 48 of a

Wake up frame 3 pattern.

Description

WF3BM3

Wake up Frame 3 Byte Mask 3. The last 16 bytes mask covering bytes 49 to 64 of a

Wake up frame 3 pattern.

Description

Reserved.

TCGICMP Transmit Checksum Generation for ICMP

When this bit is set, The KSZ8851-16MLL is enabled to transmit ICMP frame (only for

non-fragment frame) checksum generation.

Reserved.

47

KSZ8851-16MLL/MLLI

M9999-083109-2.0