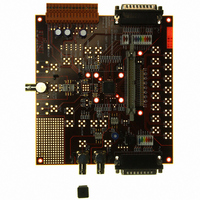

DK86060-3 Fujitsu Semiconductor America Inc, DK86060-3 Datasheet - Page 25

DK86060-3

Manufacturer Part Number

DK86060-3

Description

KIT DEV 16BIT DAC FOR MB86060

Manufacturer

Fujitsu Semiconductor America Inc

Specifications of DK86060-3

Number Of Dac's

1

Number Of Bits

16

Outputs And Type

1, Differential

Sampling Rate (per Second)

400M

Data Interface

Parallel

Dac Type

Current

Voltage Supply Source

Single

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

MB86060

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

865-1009

February 2009 Version 2.0

FME/MS/SFDAC1/DS/4250

MB86060 16-bit Interpolating Digital to Analog Converter

4.4

The data input interface is a 16-bit wide CMOS bus, operating at speeds up to 200MHz. As such this

bus can radiate large amounts of RF radiation and generate substantial ground noise problems if it

is routed for any distance across the PCB. In addition to following the PCB layout guidelines in

section 4.1, it may be possible to minimise these problems by transmitting data across the PCB as

LVDS, and only converting to CMOS locally to the DAC.

LVDS is a low-voltage differential signalling format that is becoming increasingly popular for data

transmission, and as such is now well supported by the majority of programmable logic devices. It

has a signal swing of 350mV, and a common mode level of 1.25V. As the signal is transmitted as a

differential signal, immunity to noise pick-up is very high, radiation is minimal, and a direct ground

connection is not required between transmitter and receiver.

Four 4-bit LVDS to CMOS receivers (available from a number of manufacturers) could be used to

interface the MB86060’s 16-bit data interface to an LVDS bus. Many receivers have a flow through

pin-out design, with the power supply pins and CMOS data pins on one side, and the LVDS pins on

the other side of the package. This design makes PCB ground plane layout especially easy as the

data generator and DAC PCB regions can be kept some distance apart. The data generating device

ground plane can extend to just under the LVDS pins on one side of the converters package (to

maintain track impedance of 100 ), but no further so as not to merge or connect to the DAC’s CMOS

ground plane on the other side. The CMOS data signal tracks from the converter to the DAC can now

be limited to just a few tens of millimetres. The converters 3.3V supply would be connected to the

DAC’s DVDD/DVSS supply region. See figure 14.

Copyright © 2003-2009 Fujitsu Microelectronics Europe GmbH

Disclaimer: The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before

Input Data Interfacing

ordering.The information and circuit diagrams in this document are presented “as is”, no license is granted by implication or otherwise.

FPGA

GND

D0

D0

System Ground

Figure 14 Using LVDS to CMOS Converters

100

LVDS to CMOS

Production

DVDD

DVSS

D0

DVSS

DVDD

MB86060

Page 25 of 44