CYII5SC1300-EVAL Cypress Semiconductor Corp, CYII5SC1300-EVAL Datasheet - Page 18

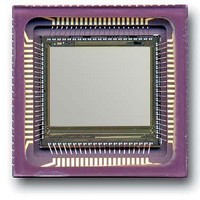

CYII5SC1300-EVAL

Manufacturer Part Number

CYII5SC1300-EVAL

Description

BOARD EVAL IMG SENS IBIS5-B-1300

Manufacturer

Cypress Semiconductor Corp

Specifications of CYII5SC1300-EVAL

Sensor Type

CMOS Imaging, Color (RGB)

Sensing Range

1.3 Megapixel

Interface

Parallel/Serial

Sensitivity

106 fps

Voltage - Supply

3 V ~ 4.5 V

Embedded

No

Utilized Ic / Part

IBIS5-B-1300

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Document #: 38-05710 Rev. *A

Synchronous Shutter: Pixel Readout

Basic Operation

Y_START and Y_CLOCK must change on the falling edge of

the SYS_CLOCK (Tsetup and Thold > 7.5 ns). The pulse width

must be a minimum of 1 clock cycle for Y_CLOCK and 3 clock

cycles for Y_START. As long as Y_CLOCK is applied, the

sequencer stays in a suspended state. (See

T

generates the control signals to sample the pixel signal and

pixel reset levels (double sampling fpn-correction), and starts

the readout of one line. The row blanking time depends on the

granularity of the X-sequencer clock (see

Table 15.Row Blanking Time as Function of X-sequencer

Granularity

Granularity

1

—Row blanking time: During this period, the X-sequencer

N

x 16

x 32

GRAN

x 4

x 8

= 35 x N

1120 x T

560 x T

140 x T

280 x T

GRAN

SYS_CLOCK

SYS_CLOCK

SYS_CLOCK

SYS_CLOCK

T

1

(µs)

x T

SYS_CLOCK

= 14.0

= 28.0

= 3.5

= 7.0

Figure 22. Synchronous Shutter: Pixel Read Out

Table

Figure

GRAN_X_SEQ

15).

MSB/LSB

22.)

00

01

10

11

Figure 23. Pixel Output

T

NROF_PIXELS register is reached. PIXEL_VALID goes high

when the internal X_SYNC signal is generated, in other words

when the readout of the pixels is started. PIXEL_VALID goes

low when the pixel counter reaches the value loaded in the

NROF_PIXELS register (after a complete row read out).

T

value loaded in the NROF_LINES register and stays high for

1 line period (until the next falling edge of Y-CLOCK).

On Y_START the left Y-shift-register of the image core is

loaded with the YL-pointer that is loaded in to register

YL_REG.

Pixel Output

The pixel signal at the PXL_OUT1 output becomes valid after

five SYS_CLOCK cycles when the internal X_SYNC (= start of

PIXEL_VALID output or external X_LOAD pulse) pulse is

asserted. (See

T

T

T

(see

2

3

1

2

3

—Pixels counted by pixel counter until the value of

—LAST_LINE goes high when the line counter reaches the

—Row blanking time (see

—5 SYS_CLOCK cycles.

—Time for new X-pointer position upload in X_REG register

“Windowing in X-direction” on page 20

Figure

23.)

Table

CYII5FM1300AB

15).

IBIS5-B-1300

for more details).

Page 18 of 42

[+] Feedback