C8051F351-GMR Silicon Laboratories Inc, C8051F351-GMR Datasheet - Page 209

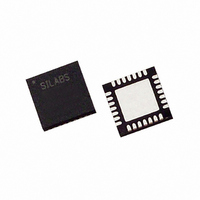

C8051F351-GMR

Manufacturer Part Number

C8051F351-GMR

Description

IC 8051 MCU 8K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F35xr

Specifications of C8051F351-GMR

Core Processor

8051

Core Size

8-Bit

Speed

50MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

17

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 8x24b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

768 B

Interface Type

I2C, SMBus, SPI, UART

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

17

Number Of Timers

4

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

KSK-SL-TOOLSTICK, PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F350DK

Minimum Operating Temperature

- 40 C

On-chip Adc

24 bit, 8 Channel

On-chip Dac

8 bit, 2 Channel

For Use With

336-1083 - DEV KIT FOR F350/351/352/353

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

- Current page: 209 of 234

- Download datasheet (2Mb)

Bit7:

Bit6:

Bit5:

Bit4:

Bit3:

Bit2:

Bit1:

Bit0:

TF3H

R/W

Bit7

TF3H: Timer 3 High Byte Overflow Flag.

Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode,

this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is

enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine.

TF3H is not automatically cleared by hardware and must be cleared by software.

TF3L: Timer 3 Low Byte Overflow Flag.

Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. When this bit is

set, an interrupt will be generated if TF3LEN is set and Timer 3 interrupts are enabled. TF3L

will set when the low byte overflows regardless of the Timer 3 mode. This bit is not automat-

ically cleared by hardware.

TF3LEN: Timer 3 Low Byte Interrupt Enable.

This bit enables/disables Timer 3 Low Byte interrupts. If TF3LEN is set and Timer 3 inter-

rupts are enabled, an interrupt will be generated when the low byte of Timer 3 overflows.

This bit should be cleared when operating Timer 3 in 16-bit mode.

0: Timer 3 Low Byte interrupts disabled.

1: Timer 3 Low Byte interrupts enabled.

UNUSED. Read = 0b. Write = don’t care.

T3SPLIT: Timer 3 Split Mode Enable.

When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.

0: Timer 3 operates in 16-bit auto-reload mode.

1: Timer 3 operates as two 8-bit auto-reload timers.

TR3: Timer 3 Run Control.

This bit enables/disables Timer 3. In 8-bit mode, this bit enables/disables TMR3H only;

TMR3L is always enabled in this mode.

0: Timer 3 disabled.

1: Timer 3 enabled.

UNUSED. Read = 0b. Write = don’t care.

T3XCLK: Timer 3 External Clock Select.

This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit

selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock

Select bits (T3MH and T3ML in register CKCON) may still be used to select between the

external clock and the system clock for either timer.

0: Timer 3 external clock selection is the system clock divided by 12.

1: Timer 3 external clock selection is the external clock divided by 8. Note that the external

oscillator source divided by 8 is synchronized with the system clock.

TF3L

R/W

Bit6

SFR Definition 22.13. TMR3CN: Timer 3 Control

TF3LEN

R/W

Bit5

R/W

Bit4

—

T3SPLIT

Rev. 1.1

R/W

Bit3

TR3

R/W

Bit2

C8051F350/1/2/3

R/W

Bit1

—

SFR Address:

T3XCLK

R/W

Bit0

0x91

00000000

Reset Value

209

Related parts for C8051F351-GMR

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc