EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 473

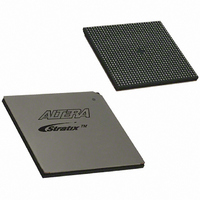

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 473 of 864

- Download datasheet (11Mb)

Introduction

Stratix I/O Banks

Altera Corporation

July 2005

S52005-3.2

To achieve high data transfer rates, Stratix devices support True-

LVDS

serializer/deserializer (SERDES) circuitry for each differential I/O pair.

Stratix SERDES circuitry transmits and receives up to 840 megabits per

second (Mbps) per channel. The differential I/O interfaces in Stratix

devices support many high-speed I/O standards, such as LVDS,

LVPECL, PCML, and HyperTransport

speed modules are designed to provide solutions for many leading

protocols such as SPI-4 Phase 2, SFI-4, 10G Ethernet XSBI, RapidIO,

HyperTransport technology, and UTOPIA-4.

The SERDES transmitter is designed to serialize 4-, 7-, 8-, or 10-bit wide

words and transmit them across either a cable or printed circuit board

(PCB). The SERDES receiver takes the serialized data and reconstructs the

bits into a 4-, 7-, 8-, or 10-bit-wide parallel word. The SERDES contains the

necessary high-frequency circuitry, multiplexer, demultiplexer, clock,

and data manipulation circuitry. You can use double data rate I/O

(DDRIO) circuitry to transmit or receive differential data in by-one (

or by-two (

1

This chapter describes the high-speed differential I/O capabilities of

Stratix programmable logic devices (PLDs) and provides guidelines for

their optimal use. You should use this document in conjunction with the

Stratix Device Family Data Sheet section of the Stratix Device Handbook,

Volume 1. Consideration of the critical issues of controlled impedance of

traces and connectors, differential routing, termination techniques, and

DC balance gets the best performance from the device. Therefore, an

elementary knowledge of high-speed clock-forwarding techniques is also

helpful.

Stratix devices contain eight I/O banks, as shown in

I/O banks on each side contain circuitry to support high-speed LVDS,

LVPECL, PCML, HSTL Class I and II, SSTL-2 Class I and II, and

HyperTransport inputs and outputs.

TM

differential I/O interfaces which have dedicated

Contact Altera Applications for more information on other B

values that the Stratix devices support and using

Quartus

B = 1 and B = 7 in

×

2) modes.

5. High-Speed Differential I/O

®

Interfaces in Stratix Devices

II software. Stratix devices currently only support

×

7 mode.

TM

technology. Stratix device high-

Figure

×

7-mode in the

5–1. The two

×

5–1

1)

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: