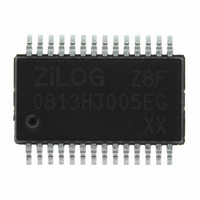

Z8F0813HJ005EG Zilog, Z8F0813HJ005EG Datasheet - Page 84

Z8F0813HJ005EG

Manufacturer Part Number

Z8F0813HJ005EG

Description

IC Z8 ENCORE MCU FLASH 8K 28SSOP

Manufacturer

Zilog

Series

Encore!® XP®r

Datasheet

1.Z8F0813PH005SC.pdf

(227 pages)

Specifications of Z8F0813HJ005EG

Core Processor

Z8

Core Size

8-Bit

Speed

5MHz

Connectivity

IrDA, UART/USART

Peripherals

Brown-out Detect/Reset, LED, POR, PWM, WDT

Number Of I /o

24

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

28-SSOP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Other names

269-4182

Z8F0813HJ005EG

Z8F0813HJ005EG

- Current page: 84 of 227

- Download datasheet (3Mb)

PS025203-0405

stored in the Timer PWM High and Low Byte registers. When the timer count value

matches the PWM value, the Timer Output toggles. The timer continues counting until it

reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon

reaching the Reload value, the timer generates an interrupt, the count value in the Timer

High and Low Byte registers is reset to

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as

a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The

Timer Output signal returns to a High (1) after the timer reaches the Reload value and is

reset to

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as

a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The

Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is

reset to

The timer also generates a second PWM output signal Timer Output Complement. The

Timer Output Complement is the complement of the Timer Output PWM signal. A pro-

grammable deadband delay can be configured to time delay (0 to 128 system clock cycles)

PWM output transitions on these two pins from a low to a high (inactive to active). This

ensures a time gap between the deassertion of one PWM output to the assertion of its com-

plement.

The steps for configuring a timer for PWM Dual Output mode and initiating the PWM

operation are as follows:

1. Write to the Timer Control register to:

2. Write to the Timer High and Low Byte registers to set the starting count value

3. Write to the PWM High and Low Byte registers to set the PWM value.

4. Write to the PWM Control register to set the PWM dead band delay value. The

5. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM

–

–

–

–

(typically

reset in PWM mode, counting always begins at the reset value of

deadband delay must be less than the duration of the positive phase of the PWM signal

(as defined by the PWM high and low byte registers). It must also be less than the

duration of the negative phase of the PWM signal (as defined by the difference

between the PWM registers and the Timer Reload registers).

period). The Reload value must be greater than the PWM value.

0001H

0001H

Disable the timer

Configure the timer for PWM Dual Output mode. Setting the mode also involves

writing to TMODEHI bit in TxCTL1 register.

Set the prescale value.

Set the initial logic level (High or Low) and PWM High/Low transition for the

Timer Output alternate function.

0001H

.

.

). This only affects the first pass in PWM mode. After the first timer

P R E L I M I N A R Y

0001H

and counting resumes.

Z8 Encore!

Product Specification

®

0001H

Z8F0823 Series

.

Timers

67

Related parts for Z8F0813HJ005EG

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: