EA-QSB-102 Embedded Artists, EA-QSB-102 Datasheet - Page 12

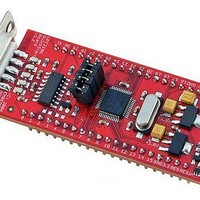

EA-QSB-102

Manufacturer Part Number

EA-QSB-102

Description

MCU, MPU & DSP Development Tools QUICKSTART PROTOTYPE BRD W/ LPC2106 RS232

Manufacturer

Embedded Artists

Specifications of EA-QSB-102

Processor To Be Evaluated

LPC2106

Data Bus Width

16 bit, 32 bit

Interface Type

RS-232, I2C, SPI, UART

Core

ARM7TDMI-S

Dimensions

27.9 mm x 65.3 mm

Maximum Operating Temperature

+ 85 C

Operating Supply Voltage

5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

NXP Semiconductors

LPC2104_2105_2106_7

Product data sheet

6.5.1 Interrupt sources

6.5 Interrupt controller

The Vectored Interrupt Controller (VIC) accepts all of the Interrupt Request (IRQ) inputs

and categorizes, them as FIQ, vectored IRQ, and non-vectored IRQ as defined by

programmable settings. The programmable assignment scheme means that priorities of

interrupts from the various peripherals can be dynamically assigned and adjusted.

Fast Interrupt reQuest (FIQ) has the highest priority. If more than one request is assigned

to FIQ, the VIC combines the requests to produce the FIQ signal to the ARM processor.

The fastest possible FIQ latency is achieved when only one request is classified as FIQ,

because then the FIQ service routine can simply start dealing with that device. But if more

than one request is assigned to the FIQ class, the FIQ service routine can read a word

from the VIC that identifies which FIQ source(s) is (are) requesting an interrupt.

Vectored IRQs have the middle priority. Sixteen of the interrupt requests can be assigned

to this category. Any of the interrupt requests can be assigned to any of the 16 vectored

IRQ slots, among which slot 0 has the highest priority and slot 15 has the lowest.

Non-vectored IRQs have the lowest priority.

The VIC combines the requests from all the vectored and non-vectored IRQs to produce

the IRQ signal to the ARM processor. The IRQ service routine can start by reading a

register from the VIC and jumping there. If any of the vectored IRQs are requesting, the

VIC provides the address of the highest-priority requesting IRQs service routine,

otherwise it provides the address of a default routine that is shared by all the non-vectored

IRQs. The default routine can read another VIC register to see what IRQs are active.

Table 4

one interrupt line connected to the Vectored Interrupt Controller, but may have several

internal interrupt flags. Individual interrupt flags may also represent more than one

interrupt source.

Table 4.

Block

WDT

-

ARM Core

ARM Core

Timer 0

Timer 1

UART 0

lists the interrupt sources for each peripheral function. Each peripheral device has

Interrupt sources

Flag(s)

Watchdog Interrupt (WDINT)

Reserved for software interrupts only

EmbeddedICE, DbgCommRx

EmbeddedICE, DbgCommTx

Match 0 to 3 (MR0, MR1, MR2, MR3)

Capture 0 to 2 (CR0, CR1, CR2)

Match 0 to 3 (MR0, MR1, MR2, MR3)

Capture 0 to 3 (CR0, CR1, CR2, CR3)

Rx Line Status (RLS)

Transmit Holding Register empty (THRE)

Rx Data Available (RDA)

Character Time-out Indicator (CTI)

Auto-Baud Time-Out (ABTO)

End of Auto-Baud (ABEO)

Rev. 07 — 20 June 2008

[1]

[1]

LPC2104/2105/2106

Single-chip 32-bit microcontrollers

© NXP B.V. 2008. All rights reserved.

VIC channel #

0

1

2

3

4

5

6

12 of 41