EA-QSB-102 Embedded Artists, EA-QSB-102 Datasheet - Page 17

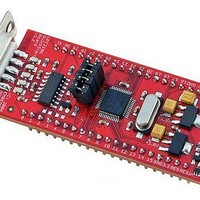

EA-QSB-102

Manufacturer Part Number

EA-QSB-102

Description

MCU, MPU & DSP Development Tools QUICKSTART PROTOTYPE BRD W/ LPC2106 RS232

Manufacturer

Embedded Artists

Specifications of EA-QSB-102

Processor To Be Evaluated

LPC2106

Data Bus Width

16 bit, 32 bit

Interface Type

RS-232, I2C, SPI, UART

Core

ARM7TDMI-S

Dimensions

27.9 mm x 65.3 mm

Maximum Operating Temperature

+ 85 C

Operating Supply Voltage

5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

NXP Semiconductors

LPC2104_2105_2106_7

Product data sheet

6.10.2 UART features available in LPC2104/2105/2106/01 only

6.11.1 Features

6.11 I

Compared to previous LPC2000 microcontrollers, UARTs in LPC2104/2105/2106/01

introduce a fractional baud rate generator for both UARTs, enabling these microcontrollers

to achieve standard baud rates such as 115200 Bd with any crystal frequency above

2 MHz. In addition, auto-CTS/RTS flow-control functions are fully implemented in

hardware.

I

and a serial data line (SDA). Each device is recognized by a unique address and can

operate as either a receiver-only device (e.g. an LCD driver or a transmitter with the

capability to both receive and send information (such as memory). Transmitters and/or

receivers can operate in either master or slave mode, depending on whether the chip has

to initiate a data transfer or is only addressed. I

controlled by more than one bus master connected to it.

The I

I

2

2

2

•

•

•

•

C is a bidirectional bus for inter-IC control using only two wires: a serial clock line (SCL),

C-bus).

•

•

•

•

•

•

•

•

•

C-bus serial I/O controller

Standard modem interface signals included on UART 1.

Fractional baud rate generator enables standard baud rates such as 115200 Bd to be

achieved with any crystal frequency above 2 MHz.

Autobauding.

Auto-CTS/RTS flow-control fully implemented in hardware.

Standard I

Easy to configure as Master, Slave or Master/Slave.

Programmable clocks allow versatile rate control.

Bidirectional data transfer between masters and slaves.

Multi-master bus (no central master).

Arbitration between simultaneously transmitting masters without corruption of serial

data on the bus.

Serial clock synchronization allows devices with different bit rates to communicate via

one serial bus.

Serial clock synchronization can be used as a handshake mechanism to suspend and

resume serial transfer.

The I

2

C-bus implemented in LPC2104/2105/2106 supports bit rate up to 400 kbit/s (Fast

2

C-bus may be used for test and diagnostic purposes.

2

C compliant bus interface.

Rev. 07 — 20 June 2008

2

LPC2104/2105/2106

C is a multi-master bus, it can be

Single-chip 32-bit microcontrollers

© NXP B.V. 2008. All rights reserved.

17 of 41