Si5369-EVB Silicon Laboratories Inc, Si5369-EVB Datasheet - Page 6

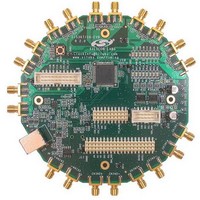

Si5369-EVB

Manufacturer Part Number

Si5369-EVB

Description

MCU, MPU & DSP Development Tools SI5369 DEV KIT

Manufacturer

Silicon Laboratories Inc

Specifications of Si5369-EVB

Processor To Be Evaluated

Si5369

Interface Type

I2C, SPI

Operating Supply Voltage

3.3 V

Lead Free Status / Rohs Status

Details

S i 5 3 6 5 / 6 6 - E V B

S i 5 3 6 7 / 6 8 - E V B

S i 5 3 6 9 - E V B

5.4. CPLD

This CPLD is required for the MCU to control an Si536x operating at either 1.8, 2.5, or 3.3 V. The CPLD provides

two main functions: it translates the voltage level from 3.3 V (the MCU voltage) to the Si536x voltage (either 1.8,

2.5, or 3.3 V). The MCU communicates to the CPLD with the SPI signals SS_CPLD_B (slave select), MISO

(master in, slave out), MOSI (master out, slave in) and SCLK. The MCU can talk to CPLD-resident registers that

are connected to pins that control the Si536x's pins, mainly for pin control mode. When the MCU wishes to access

a Si536x register, the SPI signals are passed through the CPLD, while being level translated, to the Si536x. The

CPLD is an EE device that is retains its code that is loaded through the JTAG port (J32). The core of the CPLD

runs at 1.8 V, which is provided by voltage regulator U4. The CPLD also logically connects many of the LEDs to the

appropriate Si536x pins.

5.5. MCU

The MCU communicates with the PC over USB so that PC resident software can be used to control and monitor

the Si536x. The USB connector is J6 and the debug port, by which the MCU is flashed, is J31. The reset switch,

SW1, resets the MCU, but not the CPLD. The MCU is a self-contained USB master and runs all of the code

required to control and monitor the Si536x, both in the MCU mode and in the pin-controlled modes.

U3 contains a unique serial number for each board and U5 is an EEPROM that is used to store configuration

information for the board. The board powers up in free run mode with a configuration that is outlined in "Appendix—

Powerup and Factory Default Settings" on page 26. For the pin controlled parts (Si5365/66-EVB), the contents of

U5 configure the board on power up so that jumper plugs may be used. If DSPLLsim is subsequently run, the

jumper plugs should be removed before DSPLLsim downloads the configuration to the EVB so that the jumpers do

not conflict with the CPLD outputs. For microprocessor parts, U5 configures the EVB for a specific frequency plan

as described in "Appendix—Powerup and Factory Default Settings" on page 26.

The Evaluation board has a serial port connector (J22) that supports the following:

For details, see J22 (Table 6).

Though they are not needed on this Evaluation Board because the CPLD has low output leakage current, some

applications will require the use of external pullup and pulldown resistors when three level pins are being driven by

external logic drivers. This is particularly true for the pin-controlled parts: the Si5365 and Si5367. Consult the

Si53xx-RM Any-Frequency Precision Clock Family Reference Manual for details.

LVPECL outputs will not function at 1.8 V. If the Si536x part is to be operated at 1.8 V, the output format

needs to be changed by altering either the SFOUT pins (Si5365/66) or the SFOUT register bits (Si5367/68/

69).

6

Control by the MCU/CPLD of an Any-Frequency part on an external target board.

Control of the Any-Frequency part that is on the Evaluation board through an external SPI or I

+3.3 V

MCU

Figure 3. SPI Mode Serial Data Flow

SS_CPLD_B

SCLK

MOSI

MISO

Rev. 0.5

CPLD

SS_B

SCLK

SDO

SDI

Si5367, Si5368

DUT_PWR

2

C port.