DAC1405D750/DB,598 NXP Semiconductors, DAC1405D750/DB,598 Datasheet - Page 30

DAC1405D750/DB,598

Manufacturer Part Number

DAC1405D750/DB,598

Description

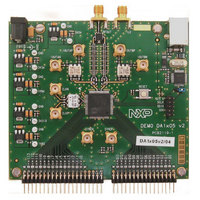

BOARD DEMO FOR DAC1405D750

Manufacturer

NXP Semiconductors

Type

D/Ar

Datasheets

1.DAC1405D750HWC15.pdf

(42 pages)

2.HSDC-ACC01DB.pdf

(32 pages)

3.ADC1415S125DB598.pdf

(2 pages)

Specifications of DAC1405D750/DB,598

Number Of Dac's

2

Number Of Bits

14

Outputs And Type

2, Differential

Sampling Rate (per Second)

750M

Data Interface

Serial, SPI™

Settling Time

20ns

Dac Type

Current

Voltage Supply Source

Analog and Digital

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

DAC1405D750

Product

Data Conversion Development Tools

Conversion Rate

750 MSPS

Resolution

14 bit

Interface Type

SMA

Supply Voltage (max)

3.3 V

Supply Voltage (min)

1.8 V

For Use With/related Products

DAC1405D750

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

568-5090

NXP Semiconductors

DAC1405D750

Product data sheet

10.11 Digital offset adjustment

Table 39.

Default settings are shown highlighted.

The settings applied to DAC_A_GAIN_FINE[5:0] (see

(address 0Ah) bit

“DAC_B_Cfg_2 register (address 0Dh) bit

full-scale current (see

Table 40.

Default settings are shown highlighted.

The coding of the fine gain adjustment is two’s complement.

When the DAC1405D750 analog output is DC connected to the next stage, the digital

offset correction can be used to adjust the common mode level at the output of the DAC. It

adds an offset at the end of the digital part, just before the DAC.

The settings applied to DAC_A_OFFSET[11:0] (see

(address 09h) bit description”

description”) and to “DAC_B_OFFSET[11:0]” (see

(address 0Ch) bit description”

description”) define the range of variation of the digital offset (see

adjustment”).

DAC_GAIN_COARSE[3:0]

Decimal

12

13

14

15

DAC_GAIN_FINE[5:0]

Decimal

32

...

0

...

31

I

I

O(fs)

O(fs)

coarse adjustment

fine adjustment

All information provided in this document is subject to legal disclaimers.

description”) and to DAC_B_GAIN_FINE[5:0] (see

Rev. 3 — 7 September 2010

Table 40 “I

Dual 14-bit DAC, up to 750 Msps; 4 and 8 interpolating

and

Binary

1100

1101

1110

1111

Two’s complement

10 0000

...

00 0000

...

01 1111

and

O(fs)

…continued

Table 21 “DAC_A_Cfg_3 register (address 0Bh) bit

Table 24 “DAC_B_Cfg_3 register (address 0Eh) bit

fine

adjustment”).

description”) define the fine variation of the

Table 22 “DAC_B_Cfg_1 register

Table 19 “DAC_A_Cfg_1 register

Table 20 “DAC_A_Cfg_2 register

DAC1405D750

I

18.5

20.0

21.0

22.0

Delta I

10.3 %

...

0

...

+10 %

O(fs)

(mA)

Table 41 “Digital offset

O(fs)

Table 23

© NXP B.V. 2010. All rights reserved.

30 of 42