P0528 Terasic Technologies Inc, P0528 Datasheet - Page 26

P0528

Manufacturer Part Number

P0528

Description

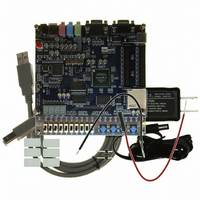

BOARD DEV DE1 ALTERA

Manufacturer

Terasic Technologies Inc

Type

FPGAr

Datasheet

1.P0528.pdf

(56 pages)

Specifications of P0528

Contents

DE1 Board, Power Supply, USB Cable, Plastic cover and software

For Use With/related Products

Cyclone II 2C20

For Use With

P0033 - BOARD ADAPTER HSMC TO GPIOP0006 - BOARD ADAPTER THDB-SUMP0001 - MODULE DIGITAL CAMERA 5MP (D5M)P0307 - KIT DEV 4.3" LCD TOUCH PANEL

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

DE1

This chapter gives instructions for using the DE1 board and describes each of its I/O devices.

4.1 Configuring the Cyclone II FPGA

The procedure for downloading a circuit from a host computer to the DE1 board is described in the

tutorial Quartus II Introduction. This tutorial is found in the DE1_tutorials folder on the DE1

System CD-ROM, and it is also available on the Altera DE1 web pages. The user is encouraged to

read the tutorial first, and to treat the information below as a short reference.

The DE1 board contains a serial EEPROM chip that stores configuration data for the Cyclone II

FPGA. This configuration data is automatically loaded from the EEPROM chip into the FPGA each

time power is applied to the board. Using the Quartus II software, it is possible to reprogram the

FPGA at any time, and it is also possible to change the non-volatile data that is stored in the serial

EEPROM chip. Both types of programming methods are described below.

The sections below describe the steps used to perform both JTAG and AS programming. For both

methods the DE1 board is connected to a host computer via a USB cable. Using this connection, the

board will be identified by the host computer as an Altera USB Blaster device. The process for

installing on the host computer the necessary software device driver that communicates with the

USB Blaster is described in the tutorial Getting Started with Altera's DE1 Board. This tutorial is

available on the DE1 System CD-ROM and from the Altera DE1 web pages.

Configuring the FPGA in JTAG Mode

1. JTAG programming: In this method of programming, named after the IEEE standards Joint

2. AS programming: In this method, called Active Serial programming, the configuration bit

Test Action Group, the configuration bit stream is downloaded directly into the Cyclone II

FPGA. The FPGA will retain this configuration as long as power is applied to the board;

the configuration is lost when the power is turned off.

stream is downloaded into the Altera EPCS4 serial EEPROM chip. It provides non-volatile

storage of the bit stream, so that the information is retained even when the power supply to

the DE1 board is turned off. When the board's power is turned on, the configuration data in

the EPCS4 device is automatically loaded into the Cyclone II FPGA.

Using the DE1 Board

Chapter 4

24

DE1 User Manual