XE8000EV110 Semtech, XE8000EV110 Datasheet - Page 108

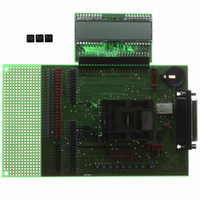

XE8000EV110

Manufacturer Part Number

XE8000EV110

Description

EVAL BOARD FOR XE8802AMI035LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV110

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC02MI035

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 108 of 193

- Download datasheet (2Mb)

The transmission format depends on the two configuration bits ClockPhase and ClockPolarity. These 2 bits

should be configured in the same way in the slave and the master device in order to properly run the SPI

transmission. The transmission baud rate depends on the two bits BaudRate, these 2 bits are only used in the

master device to generate the serial clock SCK signal at the selected frequency. Data are transferred in a duplex

way from master to slave through the MOSI wire and from slave to master through the MISO wire. Data are always

sent most significant bit first. Each SPI device sequentially operates in two times: one clock edge to sample the

received bit, and the other clock edge to shift the byte inside the shift register. The NSS signal is software

controlled. It must be driven by the SPI master device by writing to the bit NotSlaveSelect in RegSpiControl. NSS

should remain low during the byte transmission.

The next figure shows the timing diagrams for a SPI transmission with ClockPhase equal to 0. This means the

active state of the serial clock SCK signal occurs on the 2

The next figure shows the timing diagrams for a SPI transmission with ClockPhase equal to 1. This means the

active state of the serial clock SCK signal occurs on the 1

© Semtech 2006

SCK cycle

SCK

(CPOL=0)

SCK

(CPOL=1)

MOSI

MISO

NSS

Shift register

Baud Rate

Generator

Master

MSB

MSB

1

Figure 16-2: SPI transmission format with ClockPhase=0

bit 6

bit 6

2

MISO

MOSI

SCK

NSS

16-1: Connection of master and slave device

bit 5

bit 5

3

XE8802 Sensing Machine Data Acquisition MCU

bit 4

bit 4

4

bit 3

bit 3

5

16-5

nd

st

half of the SCK cycle.

half of the SCK cycle.

with ZoomingADC™ and LCD driver

bit 2

bit 2

6

MISO

MOSI

SCK

NSS

bit 1

bit 1

7

LSB

LSB

8

Shift register

Slave

www.semtech.com

Figure

Related parts for XE8000EV110

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: