XE8000EV110 Semtech, XE8000EV110 Datasheet - Page 118

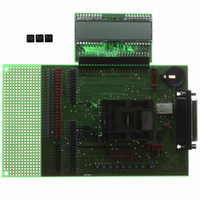

XE8000EV110

Manufacturer Part Number

XE8000EV110

Description

EVAL BOARD FOR XE8802AMI035LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV110

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC02MI035

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 118 of 193

- Download datasheet (2Mb)

Cont’

With:

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

© Semtech 2006

OUT: (r) digital output code of the analog-to-digital converter. (MSB = OUT[15])

START: (w) setting this bit triggers a single conversion (after the current one is finished). This bit always reads back 0.

SET_NELC: (rw) sets the number of elementary conversions to 2

is chopped between elementary conversions (1,2,4,8).

SET_OSR: (rw) sets the over-sampling rate (OSR) of an elementary conversion to 2

512, 1024.

CONT: (rw) setting this bit starts a conversion. A new conversion will automatically begin as long as the bit remains at 1.

TEST: bit only used for test purposes. In normal mode, this bit is forced to 0 and cannot be overwritten.

IB_AMP_ADC: (rw) sets the bias current in the ADC to 0.25*(1+ IB_AMP_ADC[1:0]) of the normal operation current (25,

50, 75 or 100% of nominal current). To be used for low-power, low-speed operation.

IB_AMP_PGA: (rw) sets the bias current in the PGAs to 0.25*(1+IB_AMP_PGA[1:0]) of the normal operation current (25,

50, 75 or 100% of nominal current). To be used for low-power, low-speed operation.

ENABLE: (rw) enables the ADC modulator (bit 0) and the different stages of the PGAs (PGAi by bit i=1,2,3). PGA stages

that are disabled are bypassed.

FIN: (rw) These bits set the sampling frequency of the acquisition chain. Expressed as a fraction of the oscillator frequency,

the sampling frequency is given as: 00

PGA1_GAIN: (rw) sets the gain of the first stage: 0

PGA2_GAIN: (rw) sets the gain of the second stage: 00

PGA3_GAIN: (rw) sets the gain of the third stage to PGA3_GAIN[6:0]⋅1/12.

PGA2_OFFSET: (rw) sets the offset of the second stage between –1 and +1, with increments of 0.2. The MSB gives the sign

(0 → positive, 1 → negative); amplitude is coded with the bits PGA2_OFFSET[5:0].

PGA3_OFFSET: (rw) sets the offset of the third stage between –5.25 and +5.25, with increments of 1/12. The MSB gives the

sign (0 → positive, 1 → negative); amplitude is coded with the bits PGA3_OFFSET[5:0].

BUSY: (r) set to 1 if a conversion is running.

DEF: (w) sets all values to their defaults (PGA disabled, max speed, nominal modulator bias current, 2 elementary

conversions, over-sampling rate of 32) and starts a new conversion without waiting the end of the preceding one.

AMUX(4:0): (rw) AMUX[4] sets the mode (0

AMUX(3) sets the sign (0

VMUX: (rw) sets the differential reference channel (0

Default values:

Default values:

Default values:

Default values:

RegAcCfg2

RegAcCfg3

RegAcCfg4

RegAcCfg5

(r = read; w = write; rw = read & write)

Register

Name

PGA1_G

BUSY

7

0

0

0

FIN[1:0]

00

straight, 1

DEF

6

0

cross) AMUX[2:0] sets the channel.

1/4 f

PGA2_GAIN[1:0]

XE8802 Sensing Machine Data Acquisition MCU

5

RC

, 01

00

4 differential inputs, 1

1, 1

R(1) and R(0), 1

1/8 f

Bit Position

4

17-6

PGA3_OFFSET[6:0]

1, 01

PGA3_GAIN[6:0]

RC

10.

AMUX[4:0]

, 10

with ZoomingADC™ and LCD driver

0000000

0000000

00000

SET_NELC[1:0]

2, 10

3

1/32 f

PGA2_OFFSET[3:0]

RC

5, 11

R(3) and R(2)).

, 11

2

. To compensate for offsets, the input signal

7 inputs with A(0) = common reference)

0000

~8kHz.

10.

(3+SET_OSR[2:0])

1

VMUX

0

0

. OSR = 8, 16, 32, ...,

www.semtech.com

Related parts for XE8000EV110

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: