DM300014 Microchip Technology, DM300014 Datasheet - Page 42

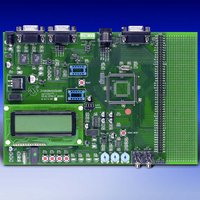

DM300014

Manufacturer Part Number

DM300014

Description

BOARD DEMO DSPICDEM 1.1 GEN PURP

Manufacturer

Microchip Technology

Datasheet

1.DM300014.pdf

(72 pages)

Specifications of DM300014

Processor To Be Evaluated

PIC30F

Data Bus Width

16 bit

Interface Type

RS-485, CAN, SPI

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

dsPICDEM™ 1.1 Development Board User’s Guide

DS70099B-page 38

Following is a summary of the processing time for each of the main demo functions.

The data is based upon a 256-sample size.

• Acquisition of 256 discrete sinewave data points sampled at 8 kHz

• FIR filtering – 72,734 instruction cycles for block processing 256 samples in a

• IIR filtering – 28,649 instruction cycles for block processing 256 samples in a

• 256-point complex FFT – 18,176 instruction cycles

• The interrupt-driven UART2 transmitter is triggered every 1.14 seconds by Timer3

• SPI 2 transmits 160 characters (80 control and 80 data) @ F

3.5.1

The overall CPU performance metric is calculated on how many complete processing

cycles can be performed over a 1 second interval. In one second, the dsPIC30F

spends the following amounts of time in each of the three major functions:

• FFT Computation:

• FIR Filter Computation:

• CPU Idle:

The 22.55 multiplier used in the above computations is based upon how many times in

one second 256 samples can be acquired and then processed by the FIR and FFT

algorithms.

For example:

• 32 mS for acquisition of 256 samples

• 9.87 mS for FIR filtering

• 2.47 mS for 256-point FFT

FIR filter specifications are listed in Table 3-5.

- Total acquisition time = 32 mS (256/8000)

273-tap band-pass filter

- 9.87 mS @ 7.3728 MIPS

9-section bi-quad bandpass filter

- 3.89 mS @ 7.3728 MIPS

- 2.47 mS @ 7.3728 MIPS

to send out approximately 145 characters.

- At 57600 baud, transmission of 145 characters requires approximately 25 mS

F

- 22.55 x 256-point complex FFTs = 55.69 mS

- 22.55 x 273-tap FIR filters = 223 mS

- Waiting for ADC data = 721 mS

Adding these three major timing metrics results in 44.34 mS. Therefore, this

44.34 mS cycle is repeated 22.55 times in a 1 second interval.

Total MIPS required = 2.1 MIPS out of available 7.3728 MIPS.

Note: Filtering and FFT operations may be interrupted by the DCI, Timer2 or

CY

Coefficients stored in program memory

= 7.3728 MHz) to the PIC18F242 LCD controller for LCD screen updates.

Performance Metric Summary with FIR Filter

UART2 modules. The time metrics presented above account for the

interrupt handler processing time from these interrupts.

Advance Information

2003 Microchip Technology Inc.

CY

/8 Hz (where