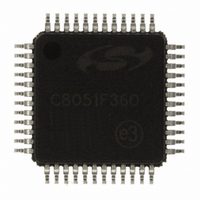

C8051F360-GQ Silicon Laboratories Inc, C8051F360-GQ Datasheet - Page 141

C8051F360-GQ

Manufacturer Part Number

C8051F360-GQ

Description

IC 8051 MCU 32K FLASH 48TQFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F36xr

Specifications of C8051F360-GQ

Program Memory Type

FLASH

Program Memory Size

32KB (32K x 8)

Package / Case

48-TQFP, 48-VQFP

Core Processor

8051

Core Size

8-Bit

Speed

100MHz

Connectivity

EBI/EMI, SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

39

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 17x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

I2C/SMBus/SPI/UART

Maximum Clock Frequency

100 MHz

Number Of Programmable I/os

39

Number Of Timers

4

Operating Supply Voltage

3 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

KSK-SL-TOOLSTICK, PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F360DK

Minimum Operating Temperature

- 40 C

On-chip Adc

21-ch x 10-bit

On-chip Dac

1-ch x 10-bit

Package

48TQFP

Device Core

8051

Family Name

C8051F36x

Maximum Speed

100 MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1483 - ADAPTER PROGRAM TOOLSTICK F360770-1006 - ISP 4PORT FOR SILABS C8051F MCU336-1412 - BOARD TARGET/PROTO W/C8051F360336-1411 - DAUGHTER CARD TOOLSTCK C8051F362336-1410 - KIT DEV FOR C8051F360 FAMILY

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1407

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F360-GQ

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

C8051F360-GQ

Manufacturer:

SILICON LABS/èٹ¯ç§‘

Quantity:

20 000

Company:

Part Number:

C8051F360-GQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

C8051F360-GQR

Manufacturer:

SILICON LABS/èٹ¯ç§‘

Quantity:

20 000

13.3.2. 16.4.2 PSWE Maintenance

13.3.3. System Clock

7. Reduce the number of places in code where the PSWE bit (b0 in PSCTL) is set to a '1'. There

8. Minimize the number of variable accesses while PSWE is set to a '1'. Handle pointer address

9. Disable interrupts prior to setting PSWE to a '1' and leave them disabled until after PSWE has

10. Make certain that the Flash write and erase pointer variables are not located in XRAM. See

11. Add address bounds checking to the routines that write or erase Flash memory to ensure that

12. If operating from an external crystal, be advised that crystal performance is susceptible to

13. If operating from the external oscillator, switch to the internal oscillator during Flash write or

should be exactly one routine in code that sets PSWE to a '1' to write Flash bytes and one rou-

tine in code that sets both PSWE and PSEE both to a '1' to erase Flash pages.

updates and loop maintenance outside the "PSWE = 1; ... PSWE = 0;" area. Code examples

showing this can be found in AN201, "Writing to Flash from Firmware", available from the Sili-

con Laboratories web site.

been reset to '0'. Any interrupts posted during the Flash write or erase operation will be ser-

viced in priority order after the Flash operation has been completed and interrupts have been

re-enabled by software.

your compiler documentation for instructions regarding how to explicitly locate variables in dif-

ferent memory areas.

a routine called with an illegal address does not result in modification of the Flash.

electrical interference and is sensitive to layout and to changes in temperature. If the system is

operating in an electrically noisy environment, use the internal oscillator or use an external

CMOS clock.

erase operations. The external oscillator can continue to run, and the CPU can switch back to

the external oscillator after the Flash operation has completed.

C8051F360/1/2/3/4/5/6/7/8/9

Rev. 1.0

141