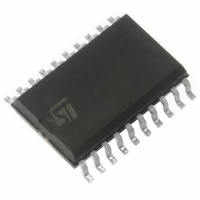

ST7FDALIF2M6 STMicroelectronics, ST7FDALIF2M6 Datasheet - Page 97

ST7FDALIF2M6

Manufacturer Part Number

ST7FDALIF2M6

Description

IC MCU 8BIT 8K 20-SOIC

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST7DALI-EVAL.pdf

(171 pages)

Specifications of ST7FDALIF2M6

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

DALI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

15

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

384 x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 5.5 V

Data Converters

A/D 7x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

20-SOIC (7.5mm Width)

Processor Series

ST7DALI

Core

ST7

Data Bus Width

8 bit

Data Ram Size

384 B

Interface Type

DALI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

15

Number Of Timers

4 bit

Operating Supply Voltage

2.4 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

ST7FLITE-SK/RAIS, ST7DALI-EVAL, ST7MDT10-DVP3, ST7MDT10-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit

For Use With

497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-2131-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST7FDALIF2M6TR

Manufacturer:

NEC

Quantity:

670

ST7DALIF2

16.11.3

16.11.4

16.11.5

Bits 7:0 = DCMFA[7:0] Forward Address.

These bits are read by software and set/cleared by hardware.

These 8 bits are used to store the "forward frame" address byte.

DCM forward data register (DCMFD)

Read only

Reset Value: 0000 0000 (00h)

Bits 7:0 = DCMFD[7:0] Forward Data.

These bits are read by software and set/cleared by hardware.

These 8 bits are used to store the "forward frame" data byte.

DCM backward data register (DCMBD)

Read / Write

Reset Value: 0000 0000 (00h)

Bits 7:0 = DCMBD[7:0] Backward Data.

These bits are set/cleared by software and cleared by hardware after a reset.

These 8 bits are used to store the "backward frame" data byte. The software writes to this

register before enabling the transmit operation.

DCM control register (DCMCR)

Read / Write

Reset Value: 0000 0000 (00h)

Bits 7:4 = Reserved. Forced by hardware to 0.

Bit 3 = DCME DALI Communication Enable.

This bit is set/cleared by software and cleared by hardware after a reset.

When set, it enables DALI communication. It also resets the entire internal finite state

machine.

0: The DCM is not enable to receive/transmit

1: The DCM is enable to receive/transmit

Bit 2 = RTA Receive/Transmit Acknowledge.

This bit is reset by hardware after it has been set by software. It is cleared after a reset.

This bit must be set, after a first DALI frame reception or transmission, to allow the DCM to

perform the next DALI communication.

0: No acknowledge

BD7

FD7

7

7

7

0

BD6

FD6

0

BD5

FD5

0

BD4

FD4

0

DCME

BD3

FD3

DALI communication module

BD2

RTA

FD2

BD1

RTS

FD1

BD0

FTS

FD0

0

0

0

97/171