ATMEGA64RZAV-10PU Atmel, ATMEGA64RZAV-10PU Datasheet - Page 23

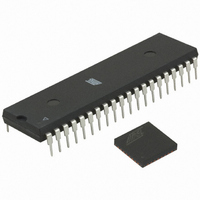

ATMEGA64RZAV-10PU

Manufacturer Part Number

ATMEGA64RZAV-10PU

Description

MCU ATMEGA644/AT86RF230 40-DIP

Manufacturer

Atmel

Series

ATMEGAr

Datasheets

1.ATMEGA644-20MU.pdf

(23 pages)

2.ATMEGA644-20MU.pdf

(376 pages)

3.AT86RF230-ZU.pdf

(98 pages)

Specifications of ATMEGA64RZAV-10PU

Frequency

2.4GHz

Modulation Or Protocol

802.15.4 Zigbee

Power - Output

3dBm

Sensitivity

-101dBm

Voltage - Supply

1.8 V ~ 3.6 V

Data Interface

PCB, Surface Mount

Memory Size

64kB Flash, 2kB EEPROM, 4kB RAM

Antenna Connector

PCB, Surface Mount

Package / Case

40-DIP (0.600", 15.24mm)

Wireless Frequency

2.4 GHz

Interface Type

JTAG, SPI

Output Power

3 dBm

For Use With

ATSTK600-TQFP32 - STK600 SOCKET/ADAPTER 32-TQFPATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK500 - PROGRAMMER AVR STARTER KIT

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Operating Temperature

-

Applications

-

Data Rate - Maximum

-

Current - Transmitting

-

Current - Receiving

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega64

7.1.2.3 TRX_OFF – Clock State

7.1.2.4 PLL_ON – PLL State

7.1.2.5 RX_ON and BUSY_RX – RX Listen and Receive State

7.1.2.6 RX_ON_NOCLK – RX Listen State without CLKM

5131E-MCU Wireless-02/09

Setting SLP_TR = L returns the radio transceiver to the TRX_OFF state. It is

recommended that pin SLP_TR should be active for a minimum of 40 CLKM cycles to

completely power down the radio transceiver.

During SLEEP state, the register contents remain valid while the content of the Frame

Buffer is cleared.

In TRX_OFF state the SPI interface and the crystal oscillator are enabled. The digital

voltage regulator (DVREG) is enabled and provides 1.8V to the digital core to make the

Frame Buffer available (see section 9.1). The microcontroller can access all digital

functions and if enabled, the CLKM output supplies a clock. The pin SLP_TR is enabled

for state control.

Entering the PLL_ON state from TRX_OFF state enables the analog voltage regulator

(AVREG) first. After the voltage regulator has been settled, the PLL frequency

synthesizer is enabled. When the PLL has been settled at the receive frequency, a

successful PLL lock is indicated by issuing a PLL_LOCK interrupt.

If an RX_ON command is issued in PLL_ON state, the receiver is immediately enabled.

If the PLL has not been settled before, actual frame reception can only happen once the

PLL has locked.

The PLL_ON state corresponds to the TX_ON state in IEEE 802.15.4.

In RX_ON state the receiver blocks and the PLL frequency synthesizer are enabled.

The AT86RF230 receive mode is internally divided into RX_ON state and BUSY_RX

state. There is no difference between these states with respect to the analog radio

transceiver circuitry, which is always turned on. During RX_ON state, only the preamble

detection of the digital signal processing is running. When a preamble and a valid SFD

are detected, also the digital receiver is turned on. The radio transceiver enters the

BUSY_RX state and a RX_START interrupt is generated.

During the frame reception frame data are stored continuously in the Frame Buffer until

the last byte was received. The completion of the frame reception is indicated by a

TRX_END interrupt and the radio transceiver reenters the state RX_ON. At the same

time the register bit RX_CRC_VALID (register 0x06) is updated with the result of the

FCS check (see section 8.2).

Note, settings of address registers 0x20 to 0x2B do not affect the frame reception in

Basic Operating Mode. Frame address filtering is only applied when using the Extended

Operating Mode (see section 7.2).

If the radio transceiver is listening for an incoming frame and the microcontroller is not

running an application, the microcontroller can be powered down to decrease the total

system power consumption. This special power-down scenario for systems running in

clock synchronous mode (see section 6.4) is supported by the AT86RF230 using the

state RX_ON_NOCLK.

This state can only be entered by setting SLP_TR = H while the AT86RF230 is in the

RX_ON state. The CLKM pin is disabled 35 clock cycles after the rising edge at the

SLP_TR pin. This allows the microcontroller to complete its power-down sequence. The

AT86RF230

23