ATMEGA64RZAV-10PU Atmel, ATMEGA64RZAV-10PU Datasheet - Page 35

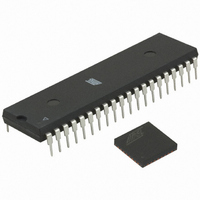

ATMEGA64RZAV-10PU

Manufacturer Part Number

ATMEGA64RZAV-10PU

Description

MCU ATMEGA644/AT86RF230 40-DIP

Manufacturer

Atmel

Series

ATMEGAr

Datasheets

1.ATMEGA644-20MU.pdf

(23 pages)

2.ATMEGA644-20MU.pdf

(376 pages)

3.AT86RF230-ZU.pdf

(98 pages)

Specifications of ATMEGA64RZAV-10PU

Frequency

2.4GHz

Modulation Or Protocol

802.15.4 Zigbee

Power - Output

3dBm

Sensitivity

-101dBm

Voltage - Supply

1.8 V ~ 3.6 V

Data Interface

PCB, Surface Mount

Memory Size

64kB Flash, 2kB EEPROM, 4kB RAM

Antenna Connector

PCB, Surface Mount

Package / Case

40-DIP (0.600", 15.24mm)

Wireless Frequency

2.4 GHz

Interface Type

JTAG, SPI

Output Power

3 dBm

For Use With

ATSTK600-TQFP32 - STK600 SOCKET/ADAPTER 32-TQFPATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK500 - PROGRAMMER AVR STARTER KIT

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Operating Temperature

-

Applications

-

Data Rate - Maximum

-

Current - Transmitting

-

Current - Receiving

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega64

AT86RF230

7.2.3.2 TX_ARET_ON – Transmit with Automatic CSMA-CA Retry

The implemented TX_ARET algorithm is shown in Figure 7-8.

The TX_ARET transaction is started by either a rising edge on SLP_TR pin or by writing

a TX_START command to register 0x02 (TRX_STATE). The radio transceiver sets the

TRAC_STATUS bits to INVALID and executes the CSMA-CA algorithm as defined by

IEEE 802.15.4-2003 section 7.5.1.4. If a clear channel is detected during CSMA-CA

execution, the radio transceiver proceeds to transmit the frame.

During frame transmission the AT86RF230 parses the frame control field of the

downloaded frame to check if an ACK reply is expected. If an ACK is expected, the

radio transceiver switches into receive mode to wait for valid ACK reply. An ACK is

considered as valid if its FCS is correct, and if the sequence number of the ACK

matches the sequence number of the previously transmitted frame.

If no valid ACK is received or a timeout (after 864 μs) occurred, the radio transceiver

retries the entire transaction, including CSMA-CA execution. This repeats until the

frame has been acknowledged or the maximum number of retransmissions (as set by

the register bits MAX_FRAME_RETRIES in register 0x2C) has been reached. In this

case, the TRX_END interrupt is issued and the value of TRAC_STATUS is set to

NO_ACK.

If a valid ACK is found, the TRX_END interrupt is issued. The Frame Pending subfield

of the ACK frame is parsed and the register bits TRAC_STATUS are updated. If the

frame pending subfield of the ACK frame is set, TRAC_STATUS is updated with

SUCCESS_DATA_PENDING, otherwise TRAC_STATUS is updated with SUCCESS.

While in receive mode for ACK reception, incoming data do not overwrite the Frame

Buffer content. Transmit data in the Frame Buffer are not changed during the TX_ARET

transaction.

If no ACK is expected, the radio transceiver issues a TRX_END interrupt after the frame

transmission has been completed. The value of register bits TRAC_STATUS (register

0x02) is set to SUCCESS.

If the CSMA-CA did not detect a clear channel, the channel access is retried as often as

specified by the register bits MAX_CSMA_RETRIES (register 0x2C). In case that

CSMA-CA does not detect a clear channel after MAX_CSMA_RETRIES, the

transaction is aborted and the TRX_END interrupt is issued. The TRAC_STATUS

register bits are updated with CHANNEL_ACCESS_FAILURE.

Note that it is recommended to download the transmit data before starting a TX_ARET

transaction.

35

5131E-MCU Wireless-02/09