A000003 Arduino, A000003 Datasheet - Page 167

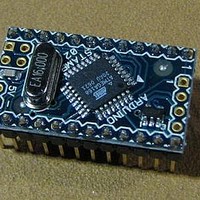

A000003

Manufacturer Part Number

A000003

Description

MCU, MPU & DSP Development Tools MINI

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000003

Processor To Be Evaluated

Atmega328

Processor Series

ATmega

Data Bus Width

8 bit

Interface Type

USB, RS-232

Operating Supply Voltage

7 V to 9 V

Contents

Board

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega168

- Current page: 167 of 378

- Download datasheet (8Mb)

18.5

18.5.1

2545S–AVR–07/10

Register Description

SPCR – SPI Control Register

• Bit 7 – SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR Register is set and the if

the Global Interrupt Enable bit in SREG is set.

• Bit 6 – SPE: SPI Enable

When the SPE bit is written to one, the SPI is enabled. This bit must be set to enable any SPI

operations.

• Bit 5 – DORD: Data Order

When the DORD bit is written to one, the LSB of the data word is transmitted first.

When the DORD bit is written to zero, the MSB of the data word is transmitted first.

• Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI mode when written to one, and Slave SPI mode when written logic

zero. If SS is configured as an input and is driven low while MSTR is set, MSTR will be cleared,

and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI Mas-

ter mode.

• Bit 3 – CPOL: Clock Polarity

When this bit is written to one, SCK is high when idle. When CPOL is written to zero, SCK is low

when idle. Refer to

marized below:

Table 18-3.

• Bit 2 – CPHA: Clock Phase

The settings of the Clock Phase bit (CPHA) determine if data is sampled on the leading (first) or

trailing (last) edge of SCK. Refer to

functionality is summarized below:

Table 18-4.

Bit

0x2C (0x4C)

Read/Write

Initial Value

CPOL

CPHA

CPOL Functionality

CPHA Functionality

0

1

0

1

SPIE

R/W

7

0

Figure 18-3

SPE

R/W

6

0

and

DORD

R/W

5

0

Figure 18-4

Figure 18-3

Leading Edge

Leading Edge

MSTR

Sample

Falling

Rising

R/W

Setup

4

0

for an example. The CPOL functionality is sum-

and

CPOL

R/W

3

0

Figure 18-4

CPHA

R/W

ATmega48/88/168

2

0

for an example. The CPOL

SPR1

R/W

1

0

Trailing Edge

Trailing Edge

Sample

Falling

Rising

Setup

SPR0

R/W

0

0

SPCR

167

Related parts for A000003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino