A000003 Arduino, A000003 Datasheet - Page 175

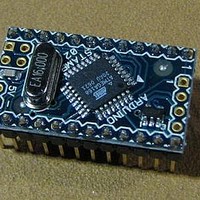

A000003

Manufacturer Part Number

A000003

Description

MCU, MPU & DSP Development Tools MINI

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000003

Processor To Be Evaluated

Atmega328

Processor Series

ATmega

Data Bus Width

8 bit

Interface Type

USB, RS-232

Operating Supply Voltage

7 V to 9 V

Contents

Board

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega168

- Current page: 175 of 378

- Download datasheet (8Mb)

19.4.1

2545S–AVR–07/10

Parity Bit Calculation

A frame starts with the start bit followed by the least significant data bit. Then the next data bits,

up to a total of nine, are succeeding, ending with the most significant bit. If enabled, the parity bit

is inserted after the data bits, before the stop bits. When a complete frame is transmitted, it can

be directly followed by a new frame, or the communication line can be set to an idle (high) state.

Figure 19-4

optional.

Figure 19-4. Frame Formats

must be

The frame format used by the USART is set by the UCSZn2:0, UPMn1:0 and USBSn bits in

UCSRnB and UCSRnC. The Receiver and Transmitter use the same setting. Note that changing

the setting of any of these bits will corrupt all ongoing communication for both the Receiver and

Transmitter.

The USART Character SiZe (UCSZn2:0) bits select the number of data bits in the frame. The

USART Parity mode (UPMn1:0) bits enable and set the type of parity bit. The selection between

one or two stop bits is done by the USART Stop Bit Select (USBSn) bit. The Receiver ignores

the second stop bit. An FE (Frame Error) will therefore only be detected in the cases where the

first stop bit is zero.

The parity bit is calculated by doing an exclusive-or of all the data bits. If odd parity is used, the

result of the exclusive or is inverted. The relation between the parity bit and data bits is as

follows:

If used, the parity bit is located between the last data bit and first stop bit of a serial frame.

St

(n)

P

Sp

IDLE

P

P

d

even

odd

n

illustrates the possible combinations of the frame formats. Bits inside brackets are

(IDLE)

St

Start bit, always low.

Data bits (0 to 8).

Parity bit. Can be odd or even.

Stop bit, always high.

No transfers on the communication line (RxDn or TxDn). An IDLE line

high.

Parity bit using even parity

Parity bit using odd parity

Data bit n of the character

P

0

P

even

odd

1

=

=

d

d

2

n 1

n 1

–

–

3

⊕

⊕

…

…

4

⊕

⊕

FRAME

[5]

d

d

3

3

⊕

⊕

[6]

d

d

2

2

⊕

⊕

[7]

d

d

1

1

[8]

⊕

⊕

ATmega48/88/168

d

d

0

0

[P]

⊕

⊕

0

1

Sp1 [Sp2]

(St / IDLE)

175

Related parts for A000003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino