AC162078 Microchip Technology, AC162078 Datasheet - Page 163

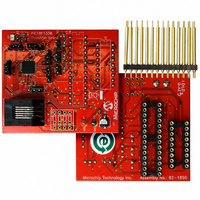

AC162078

Manufacturer Part Number

AC162078

Description

HEADER INTRFC MPLAB ICD2 18F1330

Manufacturer

Microchip Technology

Datasheet

1.AC162078.pdf

(318 pages)

Specifications of AC162078

Accessory Type

Transition Header

Lead Free Status / RoHS Status

Not applicable / Not applicable

For Use With/related Products

ICD2

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Not applicable / Not applicable

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AC162078

Manufacturer:

MICROCHIP

Quantity:

12 000

- Current page: 163 of 318

- Download datasheet (3Mb)

15.2.5

The EUSART module has the capability of sending the

special Break character sequences that are required by

the LIN/J2602 bus standard. The Break character

transmit consists of a Start bit, followed by twelve ‘0’

bits and a Stop bit. The Frame Break character is sent

whenever the SENDB and TXEN bits (TXSTA<3> and

TXSTA<5>) are set while the Transmit Shift register is

loaded with data. Note that the value of data written to

TXREG will be ignored and all ‘0’s will be transmitted.

The SENDB bit is automatically reset by hardware after

the corresponding Stop bit is sent. This allows the user

to preload the transmit FIFO with the next transmit byte

following the Break character (typically, the Sync

character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the

Break character is ignored. The write simply serves the

purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is

active or Idle, just as it does during normal

transmission. See Figure 15-10 for the timing of the

Break character sequence.

15.2.5.1

The following sequence will send a message frame

header made up of a Break, followed by an Auto-Baud

Sync byte. This sequence is typical of a LIN/J2602 bus

master.

1.

2.

FIGURE 15-10:

2009 Microchip Technology Inc.

Reg. Empty Flag)

Reg. Empty Flag)

Reg. Empty Flag)

Configure the EUSART for the desired mode.

Set the TXEN and SENDB bits to set up the

Break character.

Write to TXREG

(Transmit Buffer

(Transmit Shift

(Transmit Shift

BRG Output

(Shift Clock)

TRMT bit

TX (pin)

TXIF bit

SENDB

BREAK CHARACTER SEQUENCE

Break and Sync Transmit Sequence

SEND BREAK CHARACTER SEQUENCE

Dummy Write

SENDB Sampled Here

Start bit

bit 0

bit 1

3.

4.

5.

When the TXREG becomes empty, as indicated by the

TXIF, the next data byte can be written to TXREG.

15.2.6

The Enhanced USART module can receive a Break

character in two ways.

The first method forces configuration of the baud rate

at a frequency of 9/13 the typical speed. This allows for

the Stop bit transition to be at the correct sampling

location (13 bits for Break versus Start bit and 8 data

bits for typical data).

The second method uses the auto-wake-up feature

described in Section 15.2.4 “Auto-wake-up on Sync

Break Character”. By enabling this feature, the

EUSART will sample the next two transitions on RX/DT,

cause an RCIF interrupt and receive the next data byte

followed by another interrupt.

Note that following a Break character, the user will

typically want to enable the Auto-Baud Rate Detect

feature. For both methods, the user can set the ABDEN

bit once the TXIF interrupt is observed.

Break

Load the TXREG with a dummy character to

initiate transmission (the value is ignored).

Write ‘55h’ to TXREG to load the Sync character

into the transmit FIFO buffer.

After the Break has been sent, the SENDB bit is

reset by hardware. The Sync character now

transmits in the preconfigured mode.

PIC18F1230/1330

RECEIVING A BREAK CHARACTER

bit 11

Auto-Cleared

Stop bit

DS39758D-page 163

Related parts for AC162078

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: