AC162078 Microchip Technology, AC162078 Datasheet - Page 41

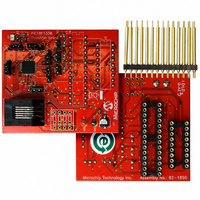

AC162078

Manufacturer Part Number

AC162078

Description

HEADER INTRFC MPLAB ICD2 18F1330

Manufacturer

Microchip Technology

Datasheet

1.AC162078.pdf

(318 pages)

Specifications of AC162078

Accessory Type

Transition Header

Lead Free Status / RoHS Status

Not applicable / Not applicable

For Use With/related Products

ICD2

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Not applicable / Not applicable

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AC162078

Manufacturer:

MICROCHIP

Quantity:

12 000

- Current page: 41 of 318

- Download datasheet (3Mb)

5.2

The MCLR pin provides a method for triggering an

external Reset of the device. A Reset is generated by

holding the pin low. These devices have a noise filter in

the MCLR Reset path which detects and ignores small

pulses.

The MCLR pin is not driven low by any internal Resets,

including the WDT.

In PIC18F1230/1330 devices, the MCLR input can be

disabled with the MCLRE Configuration bit. When

MCLR is disabled, the pin becomes a digital input. See

Section 10.1 “PORTA, TRISA and LATA Registers”

for more information.

5.3

A Power-on Reset pulse is generated on-chip

whenever V

allows the device to start in the initialized state when

V

To take advantage of the POR circuitry, tie the MCLR

pin through a resistor (1 k to 10 k) to V

eliminate external RC components usually needed to

create a Power-on Reset delay. A minimum rise rate for

V

time, see Figure 5-2.

When the device starts normal operation (i.e., exits the

Reset

(voltage, frequency, temperature, etc.) must be met to

ensure operation. If these conditions are not met, the

device must be held in Reset until the operating

conditions are met.

Power-on Reset events are captured by the POR bit

(RCON<1>). The state of the bit is set to ‘0’ whenever

a Power-on Reset occurs; it does not change for any

other Reset event. POR is not reset to ‘1’ by any hard-

ware event. To capture multiple events, the user

manually resets the bit to ‘1’ in software following any

Power-on Reset.

2009 Microchip Technology Inc.

DD

DD

is adequate for operation.

is specified (parameter D004). For a slow rise

condition),

Master Clear (MCLR)

Power-on Reset (POR)

DD

rises above a certain threshold. This

device

operating

DD

parameters

. This will

FIGURE 5-2:

Note 1: External Power-on Reset circuit is required

V

2: R < 40 k is recommended to make sure that

3: R1 1 k will limit any current flowing into

DD

PIC18F1230/1330

D

only if the V

The diode D helps discharge the capacitor

quickly when V

the voltage drop across R does not violate

the device’s electrical specification.

MCLR from external capacitor C, in the event

of MCLR/V

Electrostatic Discharge (ESD) or Electrical

Overstress (EOS).

V

DD

R

C

EXTERNAL POWER-ON

RESET CIRCUIT (FOR

SLOW V

DD

PP

DD

R1

power-up slope is too slow.

pin breakdown, due to

powers down.

DD

PIC18FXXXX

MCLR

POWER-UP)

DS39758D-page 41

Related parts for AC162078

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: