AC162078 Microchip Technology, AC162078 Datasheet - Page 90

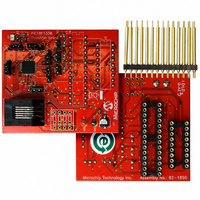

AC162078

Manufacturer Part Number

AC162078

Description

HEADER INTRFC MPLAB ICD2 18F1330

Manufacturer

Microchip Technology

Datasheet

1.AC162078.pdf

(318 pages)

Specifications of AC162078

Accessory Type

Transition Header

Lead Free Status / RoHS Status

Not applicable / Not applicable

For Use With/related Products

ICD2

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Not applicable / Not applicable

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AC162078

Manufacturer:

MICROCHIP

Quantity:

12 000

- Current page: 90 of 318

- Download datasheet (3Mb)

PIC18F1230/1330

10.2

PORTB is an 8-bit wide, bidirectional port. The

corresponding Data Direction register is TRISB. Setting

a TRISB bit (= 1) will make the corresponding PORTB

pin an input (i.e., put the corresponding output driver in

a high-impedance mode). Clearing a TRISB bit (= 0)

will make the corresponding PORTB pin an output (i.e.,

put the contents of the output latch on the selected pin).

The Output Latch register (LATB) is also memory

mapped. Read-modify-write operations on the LATB

register read and write the latched output value for

PORTB.

EXAMPLE 10-2:

Each of the PORTB pins has a weak internal pull-up. A

single control bit can turn on all the pull-ups. This is

performed by clearing bit, RBPU (INTCON2<7>). The

weak pull-up is automatically turned off when the port

pin is configured as an output. The pull-ups are

disabled on a Power-on Reset.

DS39758D-page 90

CLRF

CLRF

MOVLW

MOVWF

MOVLW

MOVWF

Note:

PORTB, TRISB and LATB

Registers

PORTB

LATB

0Fh

ADCON1 ; digital I/O pins

0CFh

TRISB

On

configured as digital inputs except for RB2

and RB3.

RB2 and RB3 are configured as analog

inputs when the T1OSCMX bit of Configu-

ration Register 3H is cleared. Otherwise,

RB2 and RB3 are also configured as

digital inputs.

a

; Initialize PORTB by

; clearing output

; data latches

; Alternate method

; to clear output

; data latches

; Set RB<4:0> as

; (required if config bit

; PBADEN is set)

; Value used to

; initialize data

; direction

; Set RB<3:0> as inputs

; RB<5:4> as outputs

; RB<7:6> as inputs

Power-on Reset,

INITIALIZING PORTB

PORTB

is

Pins RB0, RB1 and RB4:RB7 are multiplexed with the

Power Control PWM outputs.

Pins RB2 and RB3 are multiplexed with external interrupt

inputs, interrupt-on-change input, the analog comparator

inputs and the Timer1 oscillator input and output to

become

RB3/INT3/KNBI3/CMP1/T1OSI, respectively.

When the interrupt-on-change feature is enabled, only

pins configured as inputs can cause this interrupt to

occur (i.e., any RB2, RB3, RA0 and RA1 pin configured

as an output is excluded from the interrupt-on-change

comparison). The input pins (RB2, RB3, RA0 and RA1)

are compared with the old value latched on the last

read of PORTA and PORTB. The “mismatch” outputs of

these pins are ORed together to generate the RB Port

Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep mode, or

any of the Idle modes. The user, in the Interrupt Service

Routine, can clear the interrupt in the following manner:

a)

b)

c)

A mismatch condition will continue to set flag bit, RBIF.

Reading PORTB and waiting 1 T

match condition and allow flag bit, RBIF, to be cleared.

Additionally, if the port pin returns to its original state,

the mismatch condition will be cleared.

The interrupt-on-change feature is recommended for

wake-up on key depression operation and operations

where PORTA and PORTB are used for the interrupt-

on-change feature. Polling of PORTA and PORTB is

not recommended while using the interrupt-on-change

feature.

Any read or write of PORTB (except with the

MOVFF (ANY), PORTB instruction).

1 T

Clear flag bit, RBIF.

CY

RB2/INT2/KBI2/CMP2/T1OSO/T1CKI

2009 Microchip Technology Inc.

CY

will end the mis-

and

Related parts for AC162078

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: