XE8000EV101 Semtech, XE8000EV101 Datasheet - Page 104

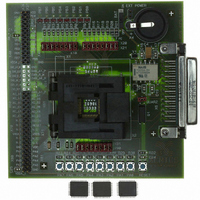

XE8000EV101

Manufacturer Part Number

XE8000EV101

Description

EVAL BOARD FOR XE8801AMI027LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV101

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC01AMI027

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Specifications (Cont’d)

© Semtech 2005

PARAMETER

POWER SUPPLY

Voltage Supply Range, V

Analog

Consumption, Total (I

Analog Power Dissipation

TEMPERATURE

Specified Range

Operating Range

Notes:

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10) Offset error is defined as the output code error for a zero volt input (ideally, output code = 0). For ± 1 LSB offset, N

(11) INL defined as the deviation of the DC transfer curve of each individual code from the best-fit straight line. This specification holds

(12) DNL is defined as the difference (in LSB) between the ideal (1 LSB) and measured code transitions for successive codes.

(13) Figures for Gains = 1 to 100. PSRR is defined as the amount of change in the ADC output value as the power supply voltage

(14) Conversion time is given by: T

(15) PGAs are reset after each writing operation to registers RegAcCfg1-5. The ADC must be started after a PGA or inputs common-mode

(16) Nominal (maximum) bias currents in PGAs and ADC, i.e. IB_AMP_PGA[1:0] = ‘11’ and IB_AMP_ADC[1:0] = ‘11’.

(17) Bias currents in PGAs and ADC set to 3/4 of nominal values, i.e. IB_AMP_PGA[1:0] = ‘10’, IB_AMP_ADC[1:0] = ‘10’.

(18) Bias currents in PGAs and ADC set to 1/2 of nominal values, i.e. IB_AMP_PGA[1:0] = ‘01’, IB_AMP_ADC[1:0] = ‘01’.

(19) Bias currents in PGAs and ADC set to 1/4 of nominal values, i.e. IB_AMP_PGA[1:0] = ‘00’, IB_AMP_ADC[1:0] = ‘00’.

ADC Only

PGA1

PGA2

PGA3

Normal Power Mode

3/4 Power Reduction Mode

1/2 Power Reduction Mode

1/4 Power Reduction Mode

Gain

V

Offset due to tolerance on GDoff

Measured with block connected to inputs through AMUX block. Normalized input sampling frequency for input impedance is f

512kHz. This figure must be multiplied by 2 for f

Figure

See equation Eq. 21 to calculate equivalent input noise.

Figure independent on PGA2 gain and sampling frequency f

equivalent input noise.

Figure independent on PGA3 gain and sampling frequency f

equivalent input noise.

Resolution is given by n = 2⋅log2(OSR) + log2(N

2, 4 or 8.

If a ramp signal is applied to the input, all digital codes appear in the resulting ADC output data.

Gain error is defined as the amount of deviation between the ideal (theoretical) transfer function and the measured transfer function

(with the offset error removed). (See Figure 16-19)

over the full scale.

changes.

be set to 1, 2, 4 or 8.

stabilisation delay. This is done by writing bit Start several cycles after PGA settings modification or channel switching. Delay between

PGA start or input channel switching and ADC start should be equivalent to OSR (between 8 and 1024) number of cycles. This delay

does not apply to conversions made without the PGAs.

IN,MAX

Quiescent

= ±(V

defined

independent

Q

)

REF

DD

/2)⋅(OSR/OSR+1).

as

Current

overall

from

CONV

2

or GDoff

+2.4

MIN

PGA1

-40

-40

PGA

= (N

ELCONV

3

gain

setting. For small intrinsic offset, use only ADC and PGA1.

gain

720/620

250/190

165/150

130/120

175/160

VALUE

3.6/1.9

2.7/1.4

1.8/0.9

0.9/0.5

⋅ (OSR + 1) + 1) / f

TYP

S

+5

ELCONV

= 256kHz, 4 for f

GD

and

). OSR can be set between 8 and 1024, in powers of 2. N

TOT

16-19

MAX

+125

+5.5

sampling

+85

=

S

S

. See model of Figure 16-18(a). See equation Eq. 21 to calculate

. See model of Figure 16-18(a) and equation Eq. 21 to calculate

S

S

GD

. OSR can be set between 8 and 1024, in powers of 2. N

= 128kHz. Input impedance is proportional to 1/f

1

⋅GD

UNITS

frequency

mW

mW

mW

mW

µA

µA

µA

µA

µA

°C

°C

V

2

⋅GD

3

.

COMMENTS/CONDITIONS

Only Acquisition Chain

V

V

V

V

V

All PGAs & ADC Active

V

V

V

V

DD

DD

DD

DD

DD

DD

DD

DD

DD

Maximum

f

= 5V/3V

= 5V/3V

= 5V/3V

= 5V/3V

= 5V/3V

= 5V/3V (Note 16)

= 5V/3V (Note 17)

= 5V/3V (Note 18)

= 5V/3V (Note 19)

S

.

See

XE8801A – SX8801R

input

model

voltage

of

www.semtech.com

ELCONV

ELCONV

Figure

S

.

is

can be set to 1,

must be ≥2.

given

ELCONV

16-18(a).

can

S

by:

=