XE8000EV101 Semtech, XE8000EV101 Datasheet - Page 37

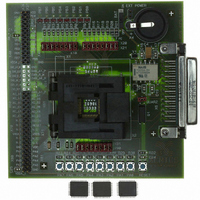

XE8000EV101

Manufacturer Part Number

XE8000EV101

Description

EVAL BOARD FOR XE8801AMI027LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV101

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC01AMI027

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 37 of 135

- Download datasheet (2Mb)

Table 6-3. RegSysWD register

6.4 Reset handling capabilities

There are 5 reset sources:

Another reset source is the bit Sleep in the RegSysReset register. This source is fully controlled by software and

is only used during the sleep mode.

Four internal reset signals are generated from these sources and distributed through the system:

For

(2) For

Table 6-4 shows a summary of the dependency of the internal reset signals on the various reset sources. In all the

tables describing the different registers, the reset source is indicated.

Table 6-4 Internal reset assertion as a function of the reset source.

© Semtech 2005

7 – 4

Pos.

Asserted

reset source

POR

RESET pin (1)

RESET pin (2)

PortA input

Watchdog

BusError

Sleep

3

2

1

0

the circuits XE8801AM/XE88LC01AM/SX8801R and XE8805AM/XE88LC05AM

(1) For the circuits XE8801AM/XE88LC01AM/SX8801R and XE8805AM/XE88LC05AM

(2) For the circuits XE88LC01 and XE88LC05

the circuits XE88LC01 and XE88LC05

RegSysWD

-

WDKey[3]

WDCounter[3]

WDKey[2]

WDCounter[2]

WDKey[1]

WDCounter[1]

WDKey[0]

WDCounter[0]

• Power On Reset (POR)

• External reset from the RESET pin

• Programmable Port A input combination

• Programmable watchdog timer reset

• Programmable BusError reset on processor access outside the allocated memory map

• resetcold:

• resetsystem: is asserted when resetcold or any other enabled reset source is active

• resetpconf:

• resetsleep:

resetsystem

Asserted

Asserted

Asserted

Asserted

Asserted

Asserted

is asserted on POR

is asserted when resetsystem is active and if the

is set. This reset is generally used in the different ports. It allows to maintain the port

configuration unchanged while the rest of the circuit is reset.

is asserted when the circuit is in sleep mode

Rw

r

w

r

w

r

w

r

w

r

-

Reset

0000

0 resetcold

0 resetcold

0 resetcold

0 resetcold

EnResPConf=0

Asserted

Asserted

when

-

-

-

-

-

Function

unused

Watchdog Key bit 3

Watchdog counter bit 3

Watchdog Key bit 2

Watchdog counter bit 2

Watchdog Key bit 1

Watchdog counter bit 1

Watchdog Key bit 0

Watchdog counter bit 0

Internal reset signals

resetpconf

EnResPConf=1

6-3

Asserted

Asserted

Asserted

Asserted

Asserted

Asserted

when

-

EnResPConf bit in the

resetsleep

Asserted

Asserted

Asserted

-

-

-

-

XE8801A – SX8801R

resetcold

Asserted

Asserted

RegSysCtrl register

-

-

-

-

-

www.semtech.com

Related parts for XE8000EV101

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: