XE8000EV101 Semtech, XE8000EV101 Datasheet - Page 20

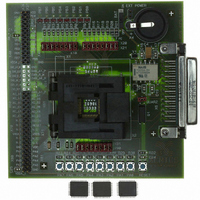

XE8000EV101

Manufacturer Part Number

XE8000EV101

Description

EVAL BOARD FOR XE8801AMI027LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV101

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC01AMI027

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 20 of 135

- Download datasheet (2Mb)

Table 3-1. CPU internal register definition

bit

7

6

5

4

3

2

1

0

Table 3-2. Status register description

The CPU also has a number of flags that can be used for conditional jumps. These flags are defined in Table 3-3.

Table 3-3. Flag description

© Semtech 2005

Register name

symbol

C

V

Z

stat

i0h

i1h

i2h

i3h

iph

name

IE2

IE1

GIE

IN2

IN1

IN0

EV1

EV0

i0l

i1l

i2l

i3l

ipl

r0

r1

r2

r3

a

name

zero

carry

overflow

function

enables (when 1) the interrupt request of level 2

enables (when 1) the interrupt request of level 1

enables (when 1) all interrupt request levels

interrupt request of level 2. The interrupts labelled “low” in the interrupt handler are

routed to this interrupt level. This bit has to be cleared when the interrupt is served.

interrupt request of level 1. The interrupts labelled “mid” in the interrupt handler are

routed to this interrupt level. This bit has to be cleared when the interrupt is served.

interrupt request of level 0. The interrupts labelled “hig” in the interrupt handler are

routed to this interrupt level. This bit has to be cleared when the interrupt is served.

event request of level 1. The events labelled “low” in the event handler are routed to

this event level. This bit has to be cleared when the event is served.

event request of level 1. The events labelled “hig” in the event handler are routed to

this event level. This bit has to be cleared when the event is served.

Register function

general purpose

general purpose

general purpose

data memory offset

MSB of the data memory index i0

LBS of the data memory index i0

MSB of the data memory index i1

LBS of the data memory index i1

MSB of the data memory index i2

LBS of the data memory index i2

MSB of the data memory index i3

LBS of the data memory index i3

MSB of the program memory index ip

LBS of the program memory index ip

status register

accumulator

function

Z=1 when the accumulator a content is zero

This flag is used in shift or arithmetic operations.

For a shift operation, it has the value of the bit that was shifted out (LSB for shift

right, MSB for shift left).

For an arithmetic operation with unsigned numbers:

This flag is used in shift or arithmetic operations.

For arithmetic or shift operations with signed numbers, it is 1 if an overflow or

underflow occurs.

it is 1 at occurrence of an overflow during an addition (or equivalent).

it is 0 at occurrence of an underflow during a subtraction (or equivalent).

3-3

XE8801A – SX8801R

www.semtech.com

Related parts for XE8000EV101

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: