XE8000EV101 Semtech, XE8000EV101 Datasheet - Page 33

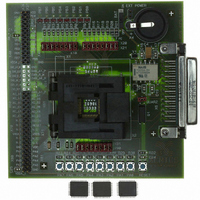

XE8000EV101

Manufacturer Part Number

XE8000EV101

Description

EVAL BOARD FOR XE8801AMI027LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV101

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC01AMI027

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 33 of 135

- Download datasheet (2Mb)

5.1 Overview

The XE8000 chips have three operating modes. There are; normal, low current and very low current modes (see

Figure 5-1). The different modes are controlled by the reset and clock blocks (see the documentation of the

respective blocks).

5.2 Operating mode

Start-up

All bits are reset in the design when a POR (power-on-reset) is active.

RC is enabled, Xtal is disabled and the CPU is reset (pmaddr = 0000).

If the port A is used to return from the sleep mode, all bits with resetcold don’t change (see sleep mode)

Reset

All bits with resetsystem and resetpconf (if enabled) are reset. Clock configuration doesn’t change except cpuck.

The CPU is reset

Active mode

This is the mode where the CPU and all peripherals can work and execute the embedded software.

Standby mode

Executing a HALT instruction moves the XE8000 into the Standby mode. The CPU is stopped, but the clocks

remain active. Therefor, the enabled peripherals remain active e.g. for time keeping. A reset or an interrupt/event

request (if enabled) cancels the standby mode.

Sleep mode

This is a very low-power mode because all circuit clocks and all peripherals are stopped. Only some service blocks

remain active. No time-keeping is possible. Two instructions are necessary to move into sleep mode. First, the

SleepEn (sleep enable) bit in RegSysCtrl has to be set to 1. The sleep mode can then be activated by setting the

Sleep bit in RegSysReset to 1.

There are three possibe ways to wake-up from the sleep mode:

Note: If the Port A is used to return from the sleep mode, all bits with resetcold don’t change (RegSysCtrl,

Note: For a lower power consumption, disable the BiasRc bit in RegSysClock before to going to sleep mode.

Note: It is recommended to insert a NOP instruction after the instruction that sets the circuit in sleep mode

© Semtech 2005

1. The por (power-on-reset caused by a power-down followed by power-on). The RAM information is lost.

2. The padreset

3. The Port A reset combination (if the Port A is present in the product). See Port A documentation for

RegSysReset (except bit sleep), EnExtClock and BiasRc in RegSysClock, RegSysRcTrim1 and

RegSysRcTrim2). The SleepFlag bit in RegSysReset, reads back a 1 if the circuit was in sleep mode

since the flag was last cleared (see reset block for more details).

The start-up time of the oscillator will then be longer however.

because this instruction can be executed when the sleep mode is left using the resetfromportA.

more details.

5-2

XE8801A – SX8801R

www.semtech.com

Related parts for XE8000EV101

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: