XE8000EV101 Semtech, XE8000EV101 Datasheet - Page 39

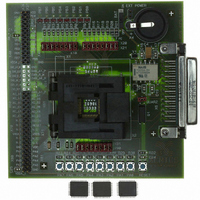

XE8000EV101

Manufacturer Part Number

XE8000EV101

Description

EVAL BOARD FOR XE8801AMI027LF

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV101

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC01AMI027

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 39 of 135

- Download datasheet (2Mb)

The last bit concerns the sleep mode control (see system documentation for the sleep mode description).

The RegSysCtrl register enables the different available reset sources and the sleep mode.

6.7 Watchdog

The watchdog is a timer which has to be cleared at least every 2 seconds by the software to prevent a reset being

generated by the timeout condition.

The watchdog can be enabled by software by setting the EnResWD bit in the RegSysCtrl register to 1. It can then

only be disabled by a power on reset.

The watchdog timer can be cleared by writing consecutively the values Hx0A and Hx03 to the RegSysWD register.

The sequence must strictly be respected to clear the watchdog.

In assembler code, the sequence to clear the watchdog is:

Only writing Hx0A followed by Hx03 resets the WD. If some other write instruction is done to the RegSysWD

between the writing of the Hx0A and Hx03 values, the watchdog timer will not be cleared.

It is possible to read the status of the watchdog in the RegSysWD register. The watchdog is a 4 bit counter with a

count range between 0 and 7. The system reset is generated when the counter is reaching the value 8.

6.8 Start-up and watchdog specifications

At start-up of the circuit, the POR (power-on-reset) block generates a reset signal during t

software execution after this period (see system chapter). The POR is intended to force the circuit in a correct state

at start-up. For precise monitoring of the supply voltage, the voltage level detector (VLD) has to be used.

© Semtech 2005

• when Sleep is set to 1, and SleepEn is 1, the sleep mode is entered. The bit always reads back a 0.

• EnResWD enables the reset due to the watchdog (can not be disabled once enabled).

• EnBusError enables the reset due to a bus error condition.

• EnResPConf enables the reset of the port configurations when reset by Port A, a Bus Error or the

• SleepEn unlocks the Sleep bit. As long as SleepEn is 0, the Sleep bit has no effect.

move AddrRegSysWD, #0x0A

move AddrRegSysWD, #0x03

watchdog.

6-5

XE8801A – SX8801R

POR

. The circuit starts

www.semtech.com

Related parts for XE8000EV101

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: