MCIMX512CJM6C Freescale Semiconductor, MCIMX512CJM6C Datasheet - Page 15

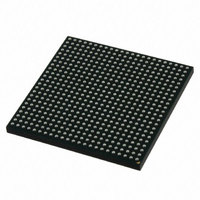

MCIMX512CJM6C

Manufacturer Part Number

MCIMX512CJM6C

Description

MULTIMEDIA PROC 529-LFBGA

Manufacturer

Freescale Semiconductor

Series

i.MX51r

Specifications of MCIMX512CJM6C

Core Processor

ARM Cortex-A8

Core Size

32-Bit

Speed

600MHz

Connectivity

1-Wire, EBI/EMI, Ethernet, I²C, IrDA, MMC, SPI, SSI, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, POR, PWM, WDT

Number Of I /o

128

Program Memory Type

ROMless

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

0.8 V ~ 1.15 V

Oscillator Type

External

Operating Temperature

-20°C ~ 85°C

Package / Case

529-LFBGA

Operating Temperature (min)

-40C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Processor Series

i.MX51

Core

ARM Cortex A8

Data Bus Width

32 bit

Program Memory Size

36 KB

Data Ram Size

128 KB

Interface Type

I2C, SPI, SSI, UART, USB

Maximum Clock Frequency

200 MHz

Number Of Timers

5

Operating Supply Voltage

0.8 V to 1.15 V

Maximum Operating Temperature

+ 95 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

MCIMX51EVKJ

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Lead Free Status / Rohs Status

Compliant

- Current page: 15 of 200

- Download datasheet (6Mb)

3.1

The NAND Flash Controller (NFC) signals are not configured in the IOMUX. The NFC interface uses

dedicated contacts on the IC.

3.2

Table 5

Only DAT0 is available when the SD/MMC is used for boot. The remaining lines (DAT1–DAT7) are not

available.

3.3

The contacts assigned to the signals used by the three I

Freescale Semiconductor

1

N/A in the ROM code indicates the pins are not available.

Signal

CD/DAT3

SDA

SCL

shows the SD/MMC IOMUX pin configuration.

Signal

DAT0

DAT1

DAT2

DAT4

DAT5

DAT6

DAT7

CMD

CLK

NAND

SD/MMC IOMUX Pin Configuration

I

2

C IOMUX Pin Configuration

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 4

SD1_DATA0.alt0

SD1_DATA3.alt0

SD1_CMD.alt0

SD1_CLK.alt0

I2C1_CLK.alt0

I2C1_DAT.alt0

eSDHC1

HSI

N/A

N/A

N/A

N/A

N/A

N/A

Table 5. SD/MMC IOMUX Pin Configuration

2

1

C

Table 6. I

2

C IOMUX Pin Configuration

SD2_DATA0.alt0

SD2_DATA3.alt0

SD2_CMD.alt0

SD2_CLK.alt0

eSDHC2

N/A

N/A

N/A

N/A

N/A

N/A

2

C modules is shown in

I2C1_CLK.alt0

I2C1_DAT.alt0

I

2

C1

NANDF_RDY_INT.alt5

NANDF_WE_B.alt2

NANDF_CS7.alt5

NANDF_RB0.alt5

eSDHC3

IOMUX Configuration for Boot Media

N/A

N/A

N/A

N/A

N/A

N/A

Table

GPIO1_3.alt2

GPIO1_2.alt2

6.

NANDF_CS2.alt5

NANDF_RB1.alt5

NANDF_CS3.alt5

NANDF_CS6.alt5

I

2

C2

eSDHC4

N/A

N/A

N/A

N/A

N/A

N/A

15

Related parts for MCIMX512CJM6C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MCIMX-LVDS1

Manufacturer:

Freescale Semiconductor

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: