A000046 Arduino, A000046 Datasheet - Page 164

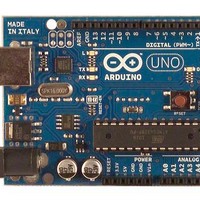

A000046

Manufacturer Part Number

A000046

Description

MCU, MPU & DSP Development Tools Uno

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000046

Processor To Be Evaluated

ATmega328

Interface Type

USB, I2C, SPI

Dimensions

2.7 in x 2.1 in

Operating Supply Voltage

5 V

Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega328

- Current page: 164 of 448

- Download datasheet (13Mb)

17.11.8

8161D–AVR–10/09

ASSR – Asynchronous Status Register

• Bit 7 – RES: Reserved bit

This bit is reserved and will always read as zero.

• Bit 6 – EXCLK: Enable External Clock Input

When EXCLK is written to one, and asynchronous clock is selected, the external clock input buf-

fer is enabled and an external clock can be input on Timer Oscillator 1 (TOSC1) pin instead of a

32 kHz crystal. Writing to EXCLK should be done before asynchronous operation is selected.

Note that the crystal Oscillator will only run when this bit is zero.

• Bit 5 – AS2: Asynchronous Timer/Counter2

When AS2 is written to zero, Timer/Counter2 is clocked from the I/O clock, clk

written to one, Timer/Counter2 is clocked from a crystal Oscillator connected to the Timer Oscil-

lator 1 (TOSC1) pin. When the value of AS2 is changed, the contents of TCNT2, OCR2A,

OCR2B, TCCR2A and TCCR2B might be corrupted.

• Bit 4 – TCN2UB: Timer/Counter2 Update Busy

When Timer/Counter2 operates asynchronously and TCNT2 is written, this bit becomes set.

When TCNT2 has been updated from the temporary storage register, this bit is cleared by hard-

ware. A logical zero in this bit indicates that TCNT2 is ready to be updated with a new value.

• Bit 3 – OCR2AUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2A is written, this bit becomes set.

When OCR2A has been updated from the temporary storage register, this bit is cleared by hard-

ware. A logical zero in this bit indicates that OCR2A is ready to be updated with a new value.

• Bit 2 – OCR2BUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2B is written, this bit becomes set.

When OCR2B has been updated from the temporary storage register, this bit is cleared by hard-

ware. A logical zero in this bit indicates that OCR2B is ready to be updated with a new value.

• Bit 1 – TCR2AUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2A is written, this bit becomes set.

When TCCR2A has been updated from the temporary storage register, this bit is cleared by

hardware. A logical zero in this bit indicates that TCCR2A is ready to be updated with a new

value.

• Bit 0 – TCR2BUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2B is written, this bit becomes set.

When TCCR2B has been updated from the temporary storage register, this bit is cleared by

hardware. A logical zero in this bit indicates that TCCR2B is ready to be updated with a new

value.

If a write is performed to any of the five Timer/Counter2 Registers while its update busy flag is

set, the updated value might get corrupted and cause an unintentional interrupt to occur.

Bit

(0xB6)

Read/Write

Initial Value

R

7

–

0

EXCLK

R/W

6

0

AS2

R/W

5

0

ATmega48PA/88PA/168PA/328P

TCN2UB

4

R

0

OCR2AUB

R

3

0

OCR2BUB

R

2

0

TCR2AUB

R

1

0

TCR2BUB

I/O

. When AS2 is

R

0

0

ASSR

164

Related parts for A000046

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino