EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 55

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

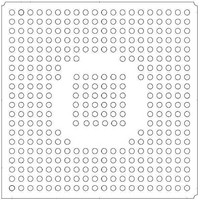

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 55 of 824

- Download datasheet (13Mb)

DS785UM1

0x8000_xxxx

0x8000_0000 - 0x8000_003C

0x8000_0040 - 0x8000_007C

0x8000_0080 - 0x8000_00BC

0x8000_00C0 - 0x8000_00FC M2P Channel 3 Registers (Rx) Memory-to-Peripheral Channel 3 Registers (Rx)

0x8000_0100 - 0x8000_013C

2.3.6 Internal Register Map

2.3.6.1 Memory Access Rules

Table 2-8 on page 2-17

their default state by the

registers are reset only by the

specified.

Any memory address not specifically assigned to a register should be avoided. Reads to

register memory addresses labelled Reserved, Unused or Undefined will return

indeterminate data. Writes to register memory addresses labelled Reserved, Unused or

Undefined are generally ignored, but this behavior is not guaranteed. Many register

addresses are not fully decoded, so aliasing may occur. Addresses and memory ranges

listed as Reserved (RSVD) should not be accessed; behavior resulting from accesses to

these regions is not defined.

The SW Lock field identifies registers with a software lock. A software lock prevents the

register from being written (unless an unlock operation is performed immediately prior to the

write). Any register whose accidental alteration could cause system damage may be

controlled with a software lock. Each peripheral with software lock capability has its own

software lock register.

Within a register definition, a reserved bit indicated by the name RSVD, means the bit is not

accessible. Software should mask the RSVD bits when doing bit reads. RSVD bits will ignore

writes, that is writing a zero or a one has no affect.

Register bits identified as NC are functionally alive but have an undocumented or a “don’t

care” operating function. Bits identified as NC must be treated in a specific manner for reads

and writes. The register descriptions will provide information on how to handle NC bits.

Unless specified otherwise, all registers can be accessed as a byte, half-word, or word.

Address

Note: The shaded memory areas are dedicated to system registers. Details of these registers

are in

CAUTION: Some memory locations are listed as Reserved. These memory locations

should not be accessed. Reading from these memory locations will yield invalid data.

Writing to these memory locations may cause unpredictable results.

Table

M2P Channel 0 Registers (Tx)

M2P Channel 1 Registers (Rx) Memory-to-Peripheral Channel 1 Registers (Rx)

M2P Channel 2 Registers (Tx)

M2M Channel 0 Registers

2-8.

Register Name

shows the memory map for internal registers. Registers are set to

RSTOn

DMA

Table 2-8. Internal Register Map

Copyright 2007 Cirrus Logic

PRSTn

pin input or by the

pin. All registers are read/write unless otherwise

Memory-to-Peripheral Channel 0 Registers (Tx)

Memory-to-Peripheral Channel 2 Registers (Tx)

Memory-to-Memory Channel 0 Registers

ARM920T Core and Advanced High-Speed Bus (AHB)

PRSTn

DMA Control Registers

Register Description

pin input. Some state conserving

EP93xx User’s Guide

Lock

SW

2-17

N

N

N

N

N

2

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc