EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 73

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

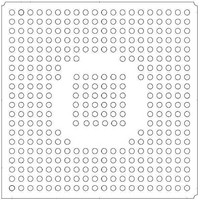

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 73 of 824

- Download datasheet (13Mb)

DS785UM1

3.1.3 Pipelines and Latency

3.1.4 Data Registers

Note that the division by zero exception is not supported as the MaverickCrunch co-

processor does not provide division or square root.

There are two primary pipelines within the MaverickCrunch co-processor. One handles all

communication with the ARM920T, while the other, the “data path” pipeline, handles all

arithmetic operations (this one actually operates at one half the MaverickCrunch co-

processor clock frequency).

The data path pipeline may run synchronously or asynchronously with respect to the ARM

instruction pipeline. If run asynchronously, data path computation is decoupled from the ARM,

allowing high throughput, though arithmetic exceptions are not synchronous. If run

synchronously, exceptions are synchronous, but throughput suffers.

Assuming no inter-instruction dependencies causing pipeline stalls, arithmetic instructions

can produce a new result every two ARM920T clocks, which is a maximum throughput of one

data path instruction per eight ARM920T clocks. The only exception is 64-bit multiplies

(CFMULD or CFMUL64), which require six extra ARM920T clocks to produce their result,

which is maximum throughput of eight ARM920T clocks per instruction.

The normal latency for an arithmetic instruction is approximately nine ARM920T clocks, from

initial decode to the time the result is written to the register file. A 64-bit multiply requires 15

clocks.

The MaverickCrunch co-processor contains these registers:

A single precision floating point value is stored in the upper 32 bits of a 64-bit register and

must be explicitly promoted to double precision to be used in double precision calculations:

• Inexact

• Sixteen 64-bit general purpose registers, c0 through c15

• Four 72-bit accumulators, a0 through a3

• One status and control register, DSPSC

Opcode

Sign Exponent

63

62

55

Copyright 2007 Cirrus Logic

Significand

32 31

MaverickCrunch Co-Processor

not used

EP93xx User’s Guide

3-3

0

3

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc