EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 601

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

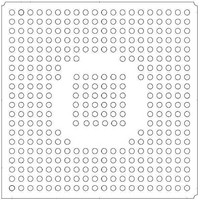

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 601 of 824

- Download datasheet (13Mb)

DS785UM1

17.3.2.2.3 Sending Packets Which are Not a Multiple of 4 Bytes In Length

17.3.2.2.4 End of Frame Interrupt

17.3.2.2.5 Disable Transmit Circuitry

17.3.2.2.6 Error conditions

17.3.2.3.1 Initialization

17.3.2.3 Receiving Data

The transmit FIFO is 32 bits wide. When using polling or interrupts to effect the transfer,

loading the FIFO with less than 32 bits would cause extraneous zero bits to be transmitted.

This issue is taken care of automatically by the DMA, so no special action is required.

However in the case of polling or interrupt-driven transfers, the IrDataTail register is the

mechanism used to preload the last 1, 2 or 3 bytes of a frame. When the transfer is complete

and the FIFO is empty, any bytes stored in the IrDataTail register are transmitted before the Ir

encoder sends the CRC and end-of-frame flags. There are three distinct addresses to which

the end of frame data is written. This allows a single word write to specify the data to be

transmitted and the number of trailing bytes to send If there is a single trailing byte to

transmit, write to address offset 0x014, for two bytes write to 0x018, and if there are three

trailing bytes write to 0x01C. (See

Once all the data sent to the FIFO has been taken by the Ir interface, the FIFO will underrun.

When this occurs any data that has been preloaded into the IrDataTail register will be used

and the Transmitted Frame Complete (TFC) interrupt will be generated.

To save power, the Transmit Enable (TXE) bit can be cleared in the IrEnable register if there

are no frames that need to be sent.

Transmitted frame abort is only signalled if IrCon register bit TUS is set to 1.

The end of a reception frame will cause an interrupt, which may be masked using the mask

register (MIMR/FIMR). The end of frame interrupt occurs after the last data value has been

transferred, including any odd bytes in the frame tail.

The following settings are required:

Bytes to transmit

Address Matching To use Address Match filtering, set the local 8 bit address

Table 17-2. Address Offsets for End-of-Frame Data

1

2

3

Copyright 2007 Cirrus Logic

in the Address Match Value Register and set the Address

Match Enable bit in the IrCon register.

Table

17-2.)

Address offset to use

0x01C

0x014

0x018

EP93xx User’s Guide

IrDA

17-5

17

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc