EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 776

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

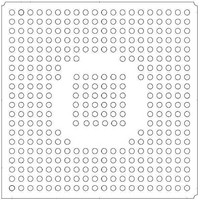

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 776 of 824

- Download datasheet (13Mb)

27

27-6

IDE Interface

EP93xx User’s Guide

27.2.6 UDMA Example

Machine sees that the incoming versus outgoing data rate is out of balance, it will signal the

controlling device to pause the transfer. For both read and write operations it is expected that

the DMA controller will get behind and not be able to keep up with the device transfer rate.

Thus the net transfer rate is determined by the available DMA controller bandwidth and how

fast the DMA completion is acknowledged by interrupt or by reading some DMA transfer

counters. The DMA controller does a DMA data transfer by:

No burst transfer is allowed.

For an estimation of the speed of operation, consider a UDMA read operation. After being

granted master status on the AHB bus, the DMA controller access to the IDEUDMADataIn

register will complete in 2 AHB clock cycles. Typical data transfers are to system dynamic

memory through the SDRAM controller. Single cycle writes to SDRAM get posted and are

completed in 2 AHB cycles, provided that the SDRAM controller is not busy. Consecutive

SDRAM single transfer writes will take 8 AHB cycles. If we assume one clock cycle for bus

arbitration, we end up with a maximum sustained DMA transfer rate of one 32-bit transfer

every 11 AHB clocks. For a 100 MHz AHB (10 ns cycle time), and two 16-bit IDE transfers

per DMA transfer, this example works out to 55 ns per IDE transfer peak rate.

A more typical DMA exists when the DMA request conflicts with ARM Core cache line fills or

raster display memory access. Cache line fills use quad word bursts and raster accesses use

16 word bursts. The worst case is the raster, which will hold the SDRAM controller for 20 AHB

clocks. Assuming a worst case system load where raster is getting 50% of the memory

bandwidth, and each raster burst in between is a cache line fill, the DMA controller can only

get 12 of the 40 available clocks. In this case, the DMA write would get posted, and flushed,

but a read would use 8 of the 12 cycles. Either case would be able to complete one DMA

transfer every 40 AHB clocks. The IDE transfer rate for this example is 400 ns per DMA

transfer, which is 200 ns per IDE transfer. This still nets 10 megabytes per second (MBps) in

a heavily loaded system.

In this last example, the DMA controller would not keep up with the IDE device and the

transfers would rely on proper signaling to pause the IDE transfers until the DMA catches up.

An additional overhead would be how fast the DMA controller is configured to do another

DMA transfer after finishing one. There might be the possibility that the request line has been

pulled high even before the DMA controller is set to service this request after the completion

of the previous request is acknowledged.

The device operates asynchronously to the host and all input signals to the host are

synchronized to the AHB clock. In a UDMA read operation, there is a possibility that the

device is transmitting the data and toggling DSTROBE too quickly for the host to keep up with

latching the data from DD bus, based on the synchronized version of DSTROBE. There is a

lower limit for AHB clock speed, where lowering the speed further cannot guarantee correct

• Requesting the AHB

• Reading the source data to a local buffer

• Requests the AHB for the write to the destination.

Copyright 2007 Cirrus Logic

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc