Si5369-EVB Silicon Laboratories Inc, Si5369-EVB Datasheet - Page 35

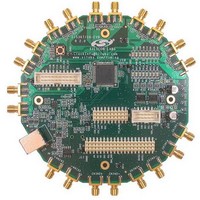

Si5369-EVB

Manufacturer Part Number

Si5369-EVB

Description

MCU, MPU & DSP Development Tools SI5369 DEV KIT

Manufacturer

Silicon Laboratories Inc

Specifications of Si5369-EVB

Processor To Be Evaluated

Si5369

Interface Type

I2C, SPI

Operating Supply Voltage

3.3 V

Lead Free Status / Rohs Status

Details

- Current page: 35 of 84

- Download datasheet (871Kb)

Reset value = 0010 1100

Register 19.

Name

Type

6:5

4:3

2:0

Bit

Bit

7

FOS_THR [1:0] FOS_THR [1:0].

VALTIME [1:0]

FOS_EN

LOCKT [2:0]

R/W

FOS_EN

D7

Name

D6

FOS_THR [1:0]

FOS_EN.

Frequency offset enable globally disables FOS. See the individual FOS enables

(FOSx_EN, register 139).

00: FOS disable

01: FOS enabled by FOSx_EN

Frequency Offset at which FOS is declared:

00: ± 11 to 12 ppm Stratum 3/3E compliant, with a Stratum 3/3E used for REFCLK.

01: ± 48 to 49 ppm (SMC).

10: ± 30 ppm SONET Minimum Clock (SMC), with a Stratum 3/3E used for REFCLK.

11: ± 200 ppm

VALTIME [1:0].

Sets amount of time for input clock to be valid before the associated alarm is removed.

00: 2 ms

01: 100 ms

10: 200 ms

11: 13 s

LOCKT [2:0].

Sets retrigger interval for one shot monitoring phase detector output. One shot is trig-

gered by phase slip in DSPLL. Refer to the Family Reference Manual for more details.

000: 106 ms

001: 53 ms

010: 26.5 ms

011: 13.3 ms

100: 6.6 ms

101: 3.3 ms

110: 1.66 ms

111: 833 µs

R/W

D5

Preliminary Rev. 0.4

D4

VALTIME [1:0]

R/W

Function

D3

D2

LOCKT [2:0]

R/W

D1

D0

35

Related parts for Si5369-EVB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc