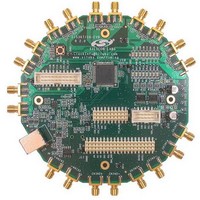

Si5369-EVB Silicon Laboratories Inc, Si5369-EVB Datasheet - Page 63

Si5369-EVB

Manufacturer Part Number

Si5369-EVB

Description

MCU, MPU & DSP Development Tools SI5369 DEV KIT

Manufacturer

Silicon Laboratories Inc

Specifications of Si5369-EVB

Processor To Be Evaluated

Si5369

Interface Type

I2C, SPI

Operating Supply Voltage

3.3 V

Lead Free Status / Rohs Status

Details

- Current page: 63 of 84

- Download datasheet (871Kb)

Reset value = 0000 0000

Register 136.

Name

Type

5:0

Bit

Bit

7

6

RST_REG

RST_REG

Reserved

Name

R/W

ICAL

D7

RST_REG.

Internal Reset.

0: Normal operation.

1: Reset of all internal logic. Outputs tristated or disabled during reset.

ICAL.

Start an Internal Calibration Sequence.

For proper operation, the device must go through an internal calibration sequence. ICAL

is a self-clearing bit. Writing a one to this location initiates an ICAL. The calibration is

complete once the LOL alarm goes low. A valid stable clock (within 100 ppm) must be

present to begin ICAL.

Note: Any divider, CLKINn_RATE or BWSEL_REG changes require an ICAL to take effect.

0: Normal operation.

1: Writing a "1" initiates internal self-calibration. Upon completion of internal self-

calibration, ICAL is internally reset to zero.

ICAL

R/W

D6

Changes in SFOUTn_REG, PD_CKn, or DSBLn_REG will cause a random change in skew

until an ICAL is completed.

D5

R

Preliminary Rev. 0.4

D4

R

Function

D3

R

D2

R

D1

R

D0

R

63

Related parts for Si5369-EVB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc