XC3S250E Xilinx, Inc., XC3S250E Datasheet - Page 94

XC3S250E

Manufacturer Part Number

XC3S250E

Description

Spartan-3E FPGA Family

Manufacturer

Xilinx, Inc.

Datasheet

1.XC3S250E.pdf

(193 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

XC3S250E

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Company:

Part Number:

XC3S250E-4CP132C

Manufacturer:

XILINX

Quantity:

435

Part Number:

XC3S250E-4CP132I

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Company:

Part Number:

XC3S250E-4CPG132C

Manufacturer:

Xilinx Inc

Quantity:

10 000

Company:

Part Number:

XC3S250E-4CPG132CS1

Manufacturer:

SANYO

Quantity:

1 000

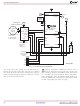

Voltage Compatibility

The 2.5V VCCAUX supply powers the JTAG interface. All of

the user I/Os are separately powered by their respective

VCCO_# supplies.

When connecting the Spartan-3E JTAG port to a 3.3V inter-

face, the JTAG input pins must be current-limited to 10 mA

or less using series resistors. Similarly, the TDO pin is a

CMOS output powered from +2.5V. The TDO output can

directly drive a 3.3V input but with reduced noise immunity.

See application note XAPP453: "The 3.3V Configuration of

Spartan-3 FPGAs" for additional information.

Maximum Bitstream Size for Daisy-Chains

The maximum bitstream length supported by Spartan-3E

FPGAs in serial daisy-chains is 4,294,967,264 bits (4

Gbits), roughly equivalent to a daisy-chain with 720

XC3S1600E FPGAs. This is a limit only for serial

daisy-chains where configuration data is passed via the

FPGA’s DOUT pin. There is no such limit for JTAG chains.

Configuration Sequence

The Spartan-3E configuration process is three-stage pro-

cess that begins after the FPGA powers on (a POR event)

DS312-2 (v1.1) March 21, 2005

Advance Product Specification

TMS

TDO

TCK

TDI

+2.5V

JTAG

R

JTAG

Mode

P

‘1’

‘0’

‘1’

HSWAP

M2

M1

M0

TDI

PROG_B

TMS

TCK

Spartan-3E

VCCINT

FPGA

+1.2V

GND

VCCAUX

Figure 62: JTAG Configuration Mode

VCCO_0

VCCO_2

DONE

TDO

www.xilinx.com

VCCO_0

VCCO_2

+2.5V

or after the PROG_B input is asserted. Power-On Reset

(POR) occurs after the V

2 supplies reach their respective input threshold levels.

After either a POR or PROG_B event, the three-stage con-

figuration process begins.

1. The FPGA clears (initializes) the internal configuration

2. Configuration data is loaded into the internal memory.

3. The user-application is activated by a start-up process.

Figure 63

configuration logic, showing the interaction of different

device inputs and Bitstream Generator (BitGen) options. A

flow diagram for the configuration sequence of the Serial

and Parallel modes appears in

the Boundary-Scan or JTAG configuration sequence.

Initialization

Configuration automatically begins after power-on or after

asserting the FPGA PROG_B pin, unless delayed using the

FPGA’s INIT_B pin. The FPGA holds the open-drain INIT_B

signal Low while it clears its internal configuration memory.

Externally holding the INIT_B pin Low forces the configura-

tion sequencer to wait until INIT_B again goes High.

memory.

JTAG

Mode

‘1’

‘0’

‘1’

P

is a generalized block diagram of the Spartan-3E

HSWAP

M2

M1

M0

TDI

TMS

TCK

PROG_B

Spartan-3E

VCCINT

+1.2V

GND

FPGA

CCINT

VCCAUX

VCCO_0

VCCO_2

, V

DONE

Figure

TDO

CCAUX

Functional Description

64.

, and the V

Figure 65

VCCO_0

VCCO_2

+2.5V

DS312-2_56_021405

CCO

TMS

TCK

shows

Bank

87