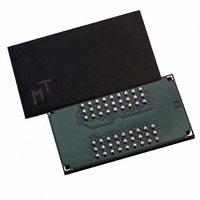

MT48H8M16LFB4-8 IT TR Micron Technology Inc, MT48H8M16LFB4-8 IT TR Datasheet - Page 13

MT48H8M16LFB4-8 IT TR

Manufacturer Part Number

MT48H8M16LFB4-8 IT TR

Description

IC SDRAM 128MBIT 125MHZ 54VFBGA

Manufacturer

Micron Technology Inc

Datasheet

1.MT48H8M16LFB4-8_IT_TR.pdf

(64 pages)

Specifications of MT48H8M16LFB4-8 IT TR

Format - Memory

RAM

Memory Type

Mobile SDRAM

Memory Size

128M (8Mx16)

Speed

125MHz

Interface

Parallel

Voltage - Supply

1.7 V ~ 1.9 V

Operating Temperature

-40°C ~ 85°C

Package / Case

54-VFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

557-1051-2

Extended Mode Register

Temperature Compensated Self Refresh

Partial Array Self Refresh

Driver Strength

PDF: 09005aef80c97087/Source: 09005aef80c97015

MT48H8M16_2.fm - Rev. E 3/05 EN

The extended mode register controls the functions beyond those controlled by the mode

register. These additional functions are special features of the mobile device. They

include temperature compensated self refresh (TCSR) control, partial array self refresh

(PASR), and output drive strength. Not programming the extended mode register upon

initialization, will result in default settings for the low power features. The extended

mode will default to the +85°C setting for TCSR, full drive strength, and full array refresh.

The extended mode register is programmed via the MODE REGISTER SET command

(BA1 = 1, BA0 = 0) and retains the stored information until it is programmed again or the

device loses power.

The extended mode register must be programmed with E6 through E11 set to “0.” It

must be loaded when all banks are idle and no bursts are in progress, and the controller

must wait the specified time before initiating any subsequent operation. Violating either

of these requirements results in unspecified operation.

Once the values are entered the extended mode register settings will be retained even

after exiting deep power-down.

Temperature compensated self refresh (TCSR) allows the controller to program the

refresh interval during self refresh mode, according to the case temperature of the

mobile device. This allows great power savings during SELF REFRESH during most oper-

ating temperature ranges. Only during extreme temperatures would the controller have

to select the maximum TCSR level. This would guarantee data during SELF REFRESH.

Every cell in the SDRAM requires refreshing due to the capacitor losing its charge over

time. The refresh rate is dependent on temperature. At higher temperatures, a capacitor

loses charge quicker than at lower temperatures, requiring the cells to be refreshed more

often. Historically, during self refresh, the refresh rate has been set to accommodate the

worst case, or highest temperature range expected.

Thus, during ambient temperatures, the power consumed during refresh was unneces-

sarily high, because the refresh rate was set to accommodate the higher temperatures.

Adjusting the refresh rate by setting E4 and E3 allows the SDRAM to accommodate more

specific temperature regions during SELF REFRESH. There are four temperature set-

tings, which will vary the SELF REFRESH current according to the selected temperature.

This selectable refresh rate will save power when the SDRAM is operating at normal tem-

peratures.

For further power savings during SELF REFRESH, the partial array self refresh (PASR)

feature allows the controller to select the amount of memory that will be refreshed dur-

ing SELF REFRESH. The refresh options are all banks (banks 0, 1, 2, and 3); two banks

(banks 0 and 1); and one bank (bank 0). Also included in the refresh options are the 1/2

bank and 1/4 bank partial array self refresh (bank 0). WRITE and READ commands occur

to any bank selected during standard operation, but only the selected banks in PASR will

be refreshed during SELF REFRESH. It is important to note that data in unused banks, or

portions of banks, will be lost when PASR is used. Data will be lost in banks 1, 2, and 3

when the one bank option is used.

Bits E5 and E6 of the extended mode register can be used to select the driver strength of

the DQ outputs. This value should be set according to the application’s requirements.

Full drive strength was carried over from standard SDRAM and is suitable to drive higher

load systems. Full drive strength is not recommended for loads under 30pF. Half drive

13

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mb: x16 Mobile SDRAM

Mode Register Definition

©2003 Micron Technology, Inc. All rights reserved.