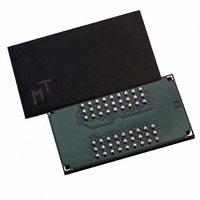

MT48H8M16LFB4-8 IT TR Micron Technology Inc, MT48H8M16LFB4-8 IT TR Datasheet - Page 20

MT48H8M16LFB4-8 IT TR

Manufacturer Part Number

MT48H8M16LFB4-8 IT TR

Description

IC SDRAM 128MBIT 125MHZ 54VFBGA

Manufacturer

Micron Technology Inc

Datasheet

1.MT48H8M16LFB4-8_IT_TR.pdf

(64 pages)

Specifications of MT48H8M16LFB4-8 IT TR

Format - Memory

RAM

Memory Type

Mobile SDRAM

Memory Size

128M (8Mx16)

Speed

125MHz

Interface

Parallel

Voltage - Supply

1.7 V ~ 1.9 V

Operating Temperature

-40°C ~ 85°C

Package / Case

54-VFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

557-1051-2

Figure 9: READ Command

PDF: 09005aef80c97087/Source: 09005aef80c97015

MT48H8M16_2.fm - Rev. E 3/05 EN

last desired data element of a longer burst that is being truncated. The new READ com-

mand should be issued x cycles before the clock edge at which the last desired data ele-

ment is valid, where x equals the CAS latency minus one.

This is shown in Figure 10, "Consecutive READ Bursts," on page 21 for CAS latencies of

two and three; data element n + 3 is either the last of a burst of four or the last desired of

a longer burst. The 128Mb SDRAM uses a pipelined architecture and therefore does not

require the 2n rule associated with a prefetch architecture. A READ command can be ini-

tiated on any clock cycle following a previous READ command. Full-speed random read

accesses can be performed to the same bank, as shown in Figure 11, "Random READ

Accesses," on page 22, or each subsequent READ may be performed to a different bank.

Data from any READ burst may be truncated with a subsequent WRITE command, and

data from a fixed-length READ burst may be immediately followed by data from a

WRITE command (subject to bus turnaround limitations). The WRITE burst may be ini-

tiated on the clock edge immediately following the last (or last desired) data element

from the READ burst, provided that I/O contention can be avoided. In a given system

design, there may be a possibility that the device driving the input data will go Low-Z

before the SDRAM DQ go High-Z. In this case, at least a single-cycle delay should occur

between the last read data and the WRITE command.

A9, A11

BA0,1

A0-A8

CAS#

RAS#

WE#

A10

CKE

CLK

CS#

HIGH

DISABLE AUTO PRECHARGE

ENABLE AUTO PRECHARGE

ADDRESS

ADDRESS

COLUMN

BANK

20

DON’T CARE

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mb: x16 Mobile SDRAM

©2003 Micron Technology, Inc. All rights reserved.

READs