MC56F8323EVM Freescale Semiconductor, MC56F8323EVM Datasheet - Page 57

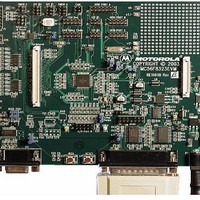

MC56F8323EVM

Manufacturer Part Number

MC56F8323EVM

Description

KIT EVALUATION FOR MC56F8323

Manufacturer

Freescale Semiconductor

Type

DSPr

Datasheets

1.CWH-UTP-ONCE-HE.pdf

(2 pages)

2.MC56F8323EVM.pdf

(72 pages)

3.MC56F8323EVME.pdf

(140 pages)

Specifications of MC56F8323EVM

Contents

Module and Misc Hardware

Processor To Be Evaluated

MC56F8322 and MC56F8323

Data Bus Width

16 bit

Interface Type

RS-232

For Use With/related Products

MC56F8322, MC56F8323

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 57 of 140

- Download datasheet (742Kb)

Part 5 Interrupt Controller (ITCN)

5.1 Introduction

The Interrupt Controller (ITCN) module is used to arbitrate between various interrupt requests (IRQs), to

signal to the 56800E core when an interrupt of sufficient priority exists, and to what address to jump in

order to service this interrupt.

5.2 Features

The ITCN module design includes these distinctive features:

For further information, see

5.3 Functional Description

The Interrupt Controller is a slave on the IPBus. It contains registers allowing each of the 82 interrupt

sources to be set to one of four priority levels, excluding certain interrupts of fixed priority. Next, all of

the interrupt requests of a given level are priority encoded to determine the lowest numerical value of the

active interrupt requests for that level. Within a given priority level, 0 is the highest priority, while number

81 is the lowest.

5.3.1

Once the ITCN has determined that an interrupt is to be serviced and which interrupt has the highest

priority, an interrupt vector address is generated. Normal interrupt handling concatenates the VBA and the

vector number to determine the vector address. In this way, an offset is generated into the vector table for

each interrupt.

5.3.2

Interrupt exceptions may be nested to allow an IRQ of higher priority than the current exception to be

serviced. The following tables define the nesting requirements for each priority level.

Freescale Semiconductor

Preliminary

•

•

•

•

Programmable priority levels for each IRQ

Two programmable Fast Interrupts

Notification to SIM module to restart clocks out of Wait and Stop modes

Drives initial address on the address bus after reset

Normal Interrupt Handling

Interrupt Nesting

1. Core status register bits indicating current interrupt mask within the core.

0

0

1

1

SR[9]

1

Table

Table 5-1 Interrupt Mask Bit Definition

0

1

0

1

4-3, Interrupt Vector Table Contents.

SR[8]

56F8323 Technical Data, Rev. 17

1

Priorities 0, 1, 2, 3

Priorities 1, 2, 3

Priorities 2, 3

Priority 3

Permitted Exceptions

None

Priority 0

Priorities 0, 1

Priorities 0, 1, 2

Masked Exceptions

Introduction

57

Related parts for MC56F8323EVM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: